通信系統中高性能分集接收機的設置

圖 2 請注意,一旦該模式被激活 1/f 噪聲(基帶附近)便被轉換為奈奎斯特,并且兩種情況下均可看到 0-1MHz 的 SNR根據奈奎斯特 (32.5MHz) 測得 65MSPS 下 ADS5282 的 SNR 為 70.4dBFS。如果假設噪聲底限較奈奎斯特扁平,那么 0-1MHz 頻帶中的噪聲功率則為 85.5dBFS,這主要是由于 15.1dB 的處理增益:10log10 (32.5M/1M)。利用能夠過濾高達 1MHz 的信號和噪聲的理想濾波器,85.5dBFS 就為數字濾波器輸出的預期 SNR。但是,1MHz 頻帶中測得的 SNR 為 81.9dBFS,因為基帶上存在 1/f 噪聲。一旦噪聲抑制模式被激活,該頻帶中測得的 SNR 便提高到 86.1dBFS。1MHz 帶寬中測量值(86.1dBFS)超出預期值(70.4+15.1=85.5dBFS)的這一事實具有誤導性,因為它是由一個標準奈奎斯特 SNR(70.4dBFS)計算得到的,而該奈奎斯特SNR 包括了高階諧波(第九階以上),其被當作了噪聲。這表明,真正的奈奎斯特 SNR(所有諧波除外)實際上高于 0.6dB,或為 71dBFS。該 ADC 還在每條通道內提供了兩倍抽取功能,以消除移頻 1/f 噪聲(仍然出現在 Fclk/2 附近),通過處理增益改善帶內SNR,并且降低高速串行 LVDS 數據速率。所用數字濾波器保持少量的抽頭,以達到節能的目的。這樣,使用抽取濾波器時處理增益為 ~2dB。通過使用抽取功能來降低 LVDS 速率后,可考慮使用更低成本的 FPGA 選項,同時在 ADC 和 FPGA 之間擁有更為輕松的時間預算。總結

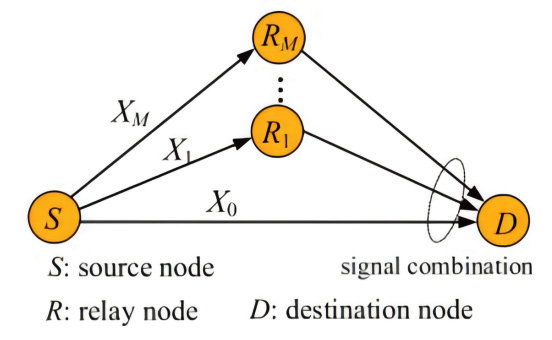

滿足蜂窩網絡規范要求的 BTS 并不是一項全新的成果。大多數新型 BTS 設計的主要目標都是想通過降低 BTS 構建成本或減少 BTS 構建數量來降低運營商的成本。其中,射頻成本只是構建蜂窩基站總成本的一部分,因此如果它們可減少構建基站的數量,那么就應該對射頻接收機設計進行改進。通過構建更為靈敏的射頻設備,覆蓋相同區域所需的基站數量更少。運用具有高度集成的 ZIF 接收機和一個八通道 ADC 的分集接收機使可實現一個更少空間占用、更低成本和更少組件數量的高性能系統。

模擬信號相關文章:什么是模擬信號

模數轉換器相關文章:模數轉換器工作原理

評論