高性能中頻采樣系統的設計與實現

2.3 采樣時鐘電路

AD9445的采樣時鐘必須是一個高質量,超低相位噪聲的時鐘源。根據上述理論分析可知,時鐘抖動會對A/D轉換器的性能造成很大影響:

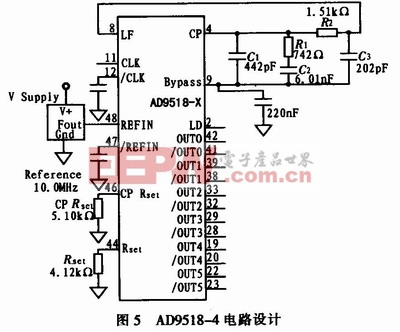

假設一個中頻輸入信號的頻率為70 MHz。采樣時鐘的抖動為1 ps,則RSN=-201g(2πx70x106x10-12)=67.13 dB。結果說明,時鐘的抖動已經將A/D轉換器的信噪比限制在67.13 dB以下。在輸入70 MHz時。如果使用一個高抖動的時鐘源,則RSN性能很容易被降低3~4 dB。這里采用高性能時鐘分配芯片AD9518-4作為采樣時鐘,電路設計如圖5所示。本文引用地址:http://www.104case.com/article/187602.htm

AD9518具有6路時鐘輸出,可分為3組,即同時可輸出3種不同頻率,并且每路的頻率輸出都可以通過軟件進行配置調節。AD9518具有內部鎖相環和壓控振蕩器電路,時鐘輸出范圍寬,時鐘抖動小,輸出頻率靈活。AD9518,我們可以獲得高性能的采樣時鐘,同時,通過對AD9518內部寄存器的操作,改變采樣時鐘的頻率,從而方便地進行中頻欠采樣或過采樣等信號處理工作。圖6顯示了本設計中時鐘采樣電路的主要性能指標。

2.4 系統電源電路

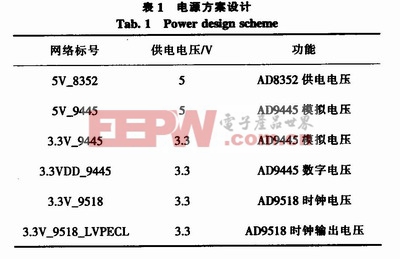

電源噪聲是板級設計中的主要噪聲來源。為了盡量減小電源噪聲,使用低壓差線性穩壓器(LDO)LT1763作為電源器件。針對運放、A/D轉換器以及時鐘電路都要嚴格滿足模擬與數字電源分離的要求。本設計中的電源方案如表1所示,每種電壓都使用1片LT1763單獨供電,從而最大限度地防止數字電壓與模擬電壓之間的串擾以及不同供電電壓之間的串擾。

3 系統軟件設計

本系統軟件設計是采樣系統的時鐘芯片AD9518的軟件配置,AD9518是一款可調時鐘輸出頻率的多路時鐘輸出芯片。其輸出時鐘可以通過對其內部寄存器的配置完成。配置軟件中的主要功能函數包括:

通過以上函數即可完成時鐘芯片的配置,達到在采樣過程中靈活變換時鐘的目的。

4 結束語

中頻采樣系統應用廣泛,但由于前端驅動設計問題或采樣時鐘抖動過大而限制采樣系統的整體性能。該設計方案已成功實現,配合后端的數字處理電路,可以獲得高性能的中頻采樣信號。

評論