MRI 架構的改進

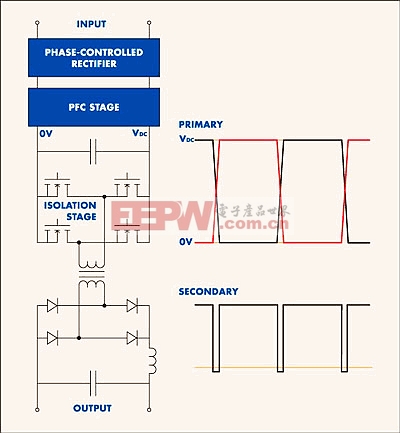

針對無線基礎設施所做的數據轉換器改進同樣能簡化這項工作。蜂窩基站對更好的噪聲與失真性能的需求,推動了能夠實現高中頻(IF)頻率采樣的高性能16位ADC的發展,而這正好也符合MRI的需求,在主流的1.5 T及3 T系統中,信號的中心頻率約為64MHz和128MHz。反觀傳統的MRI系統通常會牽涉到這樣一個問題,就是在轉換至數字域,供進一步處理之前,必須先在模擬域中下變頻至低中頻,如圖2a所示。新一代ADC的出現使這種轉換過程得以省去,進而縮小總體解決方案,如圖2b所示。這至少能部分滿足對縮小尺寸的需求,從而適合更小尺寸應用。本文引用地址:http://www.104case.com/article/187419.htm

如同任何其他的設計問題一樣,在運用新ADC技術的優勢時,也需要加以權衡。由于MRI掃描儀中的RF信號電平較低,因此信噪比(SNR)是ADC的一項關鍵特性規格。在開發突破性產品時,信噪比也是一項重要的目標特性規格。研發新功能時,諸如功耗之類的規格常常退居其次,后來的新一代ADC可以通過對主要規格的性能,例如信噪比做些讓步來實現這些次要規格。最后,隨著技術日益成熟,在第一代中達成的突破性功能,也可以在維持低功耗(或是其他次要規格)的情況下實現。因此,MRI系統設計廠商可以選擇和權衡不同ADC的強項及弱點,找出最符合其系統目標的ADC。

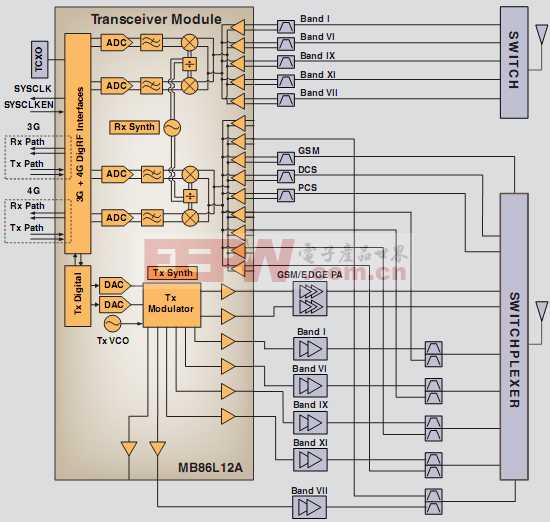

提高個別器件的性能,并不是蓬勃發展的IC技術助力實現更緊湊MRI接收架構的唯一方法,更高集成度也是受通信行業推動而發展。隨著采用模擬下變頻轉換的架構逐漸被直接采樣架構所取代,此功能也正轉換到數字領域,通常成為FPGA的一部分。信號被分成I與Q兩個分量,并且利用正交數控振蕩器(NCO)轉換至基帶,然后進行過濾;接著,此信號會傳送到系統處理器中,此時可應用更為全面的信號處理技術。

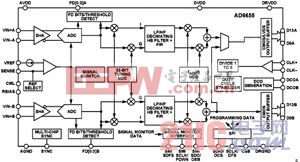

圖3 集合數模轉換器和數字下變頻功能的單芯片

這種分隔式方案可以很好地運作,然而,對于試圖使接收機解決方案尺寸最小化的設計廠商而言,具有更高集成度的解決方案會有所助益。舉例來說,高性能標準器件將模數轉換功能與針對多通道的數字下變頻功能結合到單芯片中(見圖3),這些器件可省去介于ADC與FPGA之間的高速鏈路開發需求,進而簡化設計工作。片內數字下變頻器非常靈活,能夠適應不同的系統,若將此功能從FPGA上移轉出來,便可實現更小、更簡單的FPGA設計,以節省更多空間或成本。

為滿足通信基礎設施需求所做的RF器件改進,不僅對MRI掃描儀的接收端有幫助。DAC技術的改進,特別是直接數字頻率合成(DDS)方面的改進,亦可簡化掃描時脈沖生成的設計工作。對于任何可能在未來使用到的場強,這些器件具有足堪勝任的速度。如同集成DDC能夠從FPGA上將任務移轉出來一樣,DDS元件也能夠在發射端執行相同的工作,配置為正交數字上變頻器(QDUC)的DDS具有足夠的靈活性來產生所需的脈沖。另外還有一項能夠簡化FPGA設計的特性,就是脈沖可以存儲在片上存儲器中,等到需要時再回放。

MRI系統的趨勢與其他大型系統有著相似的軌跡,例如,希望投入更少而獲益更多;希望擁有更多的接收通道,希望它能完成更多工作,但占用的空間更少,功耗更低。我們想要實現高精度的梯度控制,卻又不想采用復雜的設計方法。IC技術的持續進步不僅使上述需求的解決方案變得更為簡單,而且也預示將來還會有更多益處。

評論