高速數模轉換器AD9779/AD9788的應用

AD9779是ADI公司的一款產品,是雙通道、寬動態范圍數模轉換器(DAC),提供1 GS/s采樣速率,允許高至奈奎斯特頻率的多載波生成[1]。AD9788提供800 MS/s的采樣速率,其性能和應用方式與AD9779非常相似[2]。AD9779和AD9788雖然不是一個系列,但芯片管腳是兼容的,在硬件電路的設計上并沒有區別,兩者均使用標準的SPI接口來驅動,因此軟件實現上也可以采用統一的驅動方式。但在寄存器的配置上,兩者存在差異,這在后面會具體介紹。為了描述方便,如不特殊說明,下文中使用AD97××來統一表示AD9779和AD9788。

本文引用地址:http://www.104case.com/article/186619.htm1 AD97××的SPI規范

AD97××采用標準的4線SPI接口進行通信,當然也可以配置成3線SPI接口。

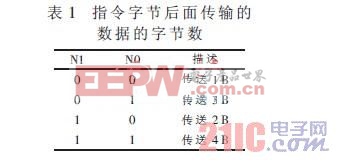

一個寄存器的讀寫周期(或叫傳輸周期)包括兩部分:指令部分和數據部分。指令部分是一個8 bit的字節,對應于8個時鐘的上升沿,用來控制讀寫以及隨后需要讀寫的數據字節數。D7為讀/寫標志位(其中讀為高,寫為低),D6和D5是用來配置指令字節后面需要傳輸的數據的字節數,通常配置如表1所示(N1和N0對應指令字節中的D6和D5),D4~D0是AD97××寄存器的地址。

需要特別說明的是,對于AD9788,指令字節的D6和D5兩個位被屏蔽了,因此這兩位不需要配置,指令字節后面需要傳輸的數據的字節數是由寄存器本身來決定的。例如對于一個32 bit的寄存器,指令字節后面需要傳輸4 B的數據。

2 AD97××的驅動方式

AD97××主要通過SPI驅動,實現寄存器的讀寫和功能的配置。

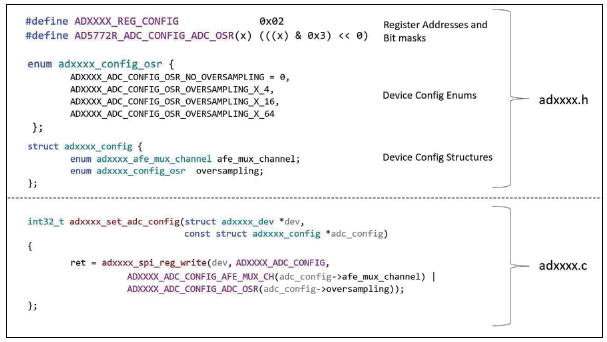

將AD97××的代碼分為兩部分設計,一部分是底層的SPI接口驅動,完成SPI接口的初始化、讀寫以及設備封裝等功能;另一部分是AD97××本身的驅動,主要通過SPI封裝的讀寫接口實現對AD97××芯片的控制。

3 AD97××的配置說明

3.1 寄存器長度不固定的問題

AD9779的寄存器長度是固定的8 bit,但AD9788的寄存器長度是不固定的,有8 bit、16 bit、32 bit,還有24 bit。datasheet中規定一個寄存器的讀寫傳輸周期由寄存器本身決定,包括一個指令字節和實際傳輸的數據字節數,例如,0x00寄存器傳輸周期為2 B,0x01寄存器傳輸周期為3 B。因此對于AD9788,不能用統一的讀寫傳輸周期,例如5 B(8 bit指令+32 bit數據),而是需要對不同長度的寄存器分開處理,這就意味著需要模擬四種不同的SPI時序。

3.2 個別寄存器回讀時應注意

在寫寄存器操作時,一般需要回讀一下來判斷寫的值是否正確。回讀時要注意以下兩種情況,否則會判斷錯誤:

(1)有的寄存器個別位是只讀的,與寫進去的值沒有關系,回讀時最好屏蔽掉相關位。例如AD9788的0x04寄存器的高三位(23 bit~21 bit)為只讀;AD9779也有類似的寄存器,例如0x00寄存器低三位(2 bit~0 bit)也是只讀;

(2)寄存器在配置完后就發生了變化,這種寄存器一般是指示寄存器,例如AD9788的0x09寄存器,有一個鎖定指示位,配置完后,若PLL鎖定,這一位會改變,讀出的值和寫的值就會不一樣。

3.3 AD97×× PLL的配置

PLL的配置是AD97××配置中的一個重點,AD9779與AD9788的PLL結構是相同的,不同的是AD9788比AD9779多了一個NCO,用于頻點搬移。本節以AD9788為例講述PLL相關寄存器的配置。

在AD9788的數據手冊中,共有15個配置寄存器,其中與PLL相關的寄存器主要有0x01、0x04兩個寄存器。不過由于要進行頻點搬移,所以還要對0x0a寄存器按照系統需要進行配置。這樣一來,只需關注0x01、0x04和0x0a這三個配置寄存器就可以了。

3.3.1 DCTL寄存器

DCTL寄存器(DIGITAL CONTROL REGISTER)參數為:地址:0x01h;寬度:2 B;默認值:0x3100;定義值:0x31c0。在此寄存器中,主要關注bit[7:6]的設置,如果系統要求DAC實現8倍內插,就要配置bit[7:6]=11,其他位按默認值即可。

3.3.2 PLLCTL寄存器

PLLCTL寄存器(PLL CONTROL REGISTER)參數為:地址:0x04h;寬度:3 B;默認值:0x3837cf;定義值:0x2fb387。

在對PLL的CTL寄存器進行設置時,主要關心bit[15:

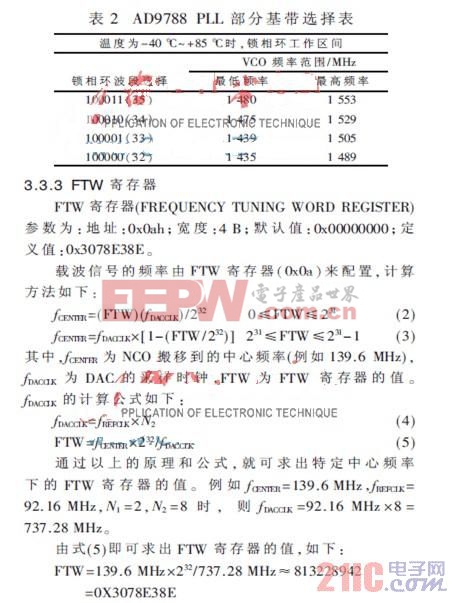

11]和bit[7:2]值的設置,bit[15]默認是PLL無效,所以要配置bit[15]=1;bit[14:13]和bit[12:11]要根據具體系統需求配置,本例中配置為bit[14:13]=01,bit[12:11]=10,bit[7:2]的值通過式(1)計算并查表2后決定。

fvco=frefclk×N1×N2 (1)

經過查表2可知,bit[7:2]可以取100001或者100000,為了使1 474.56 MHz盡量接近于PLL Lock選擇范圍的中間位置,所以選用bit[7:2]=100001。對于其他位,按器件手冊上推薦的最佳值選取即可,這里要注意bit[23:21]的只讀屬性。

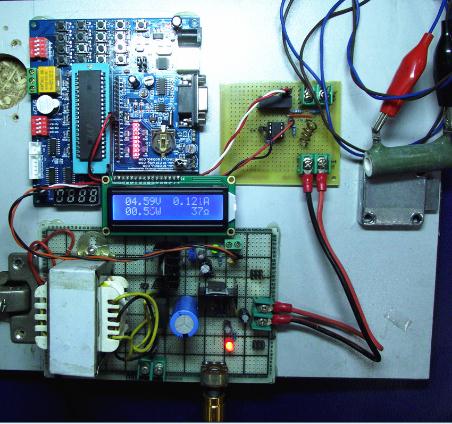

驅動工作完成以后,可以通過一些簡單的測試方法來驗證AD97××芯片是否正常工作。 當確認芯片和驅動程序能夠正常工作后,驅動程序就可以投入使用了。

評論