基于FPGA的可編程衰減器設(shè)計

引言

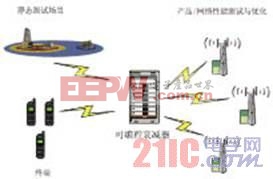

本文引用地址:http://www.104case.com/article/186355.htm可編程衰減器位于基站和終端之間,通過對射頻信號的衰減控制,實現(xiàn)對無線信號的模擬,從而實現(xiàn)對測試場景的模擬。可編程衰減器提供多個數(shù)控接口,從小到大可以構(gòu)建各個層次的測試網(wǎng)絡(luò)。所構(gòu)成的衰減矩陣通過模擬空口信道實現(xiàn)移動、切換、覆蓋等多種測試項。

衰減矩陣可作為無線性能中心實驗室的關(guān)鍵技術(shù)平臺的關(guān)鍵設(shè)備,是實現(xiàn)組網(wǎng)小區(qū)和大量終端用戶互聯(lián)通信過程的核心單元。

圖2可編程衰減器硬件結(jié)構(gòu)

圖38×8個無線通道衰減

本文介紹的可編程衰減器最高可支持8×8輸入輸出的矩陣結(jié)構(gòu),提供0~120dB的通道衰減范圍,精度達到0.5dB。

可編程衰減器設(shè)計

主要功能

可編程衰減器最高可支持8×8輸入輸出的矩陣結(jié)構(gòu),可對終端與基站之間的多個信道進行實時衰落控制,同時也能支持各類靜態(tài)測試場景長時間回放。

圖4實時衰減控制流程

圖5靜態(tài)場景回放流程

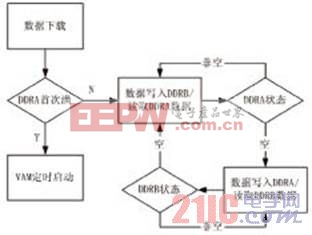

圖6乒乓結(jié)構(gòu)狀態(tài)機

硬件結(jié)構(gòu)

可編程衰減器由CPU板和IO板構(gòu)成。CPU板主要由CPU小系統(tǒng)和FPGA組成,CPU板通過FPGA-CycloneII集中控制外接的IO板。IO板的功能主要是采用FPGA-LFXP10控制數(shù)控衰減器衰減量,實現(xiàn)對無線信道衰落的模擬,從而實現(xiàn)對測試場景的模擬。

每個IO板有8個衰減通道,每個衰減通道由4個衰減范圍為31.5dB的數(shù)控衰減器構(gòu)成。一個CPU板可外接8個IO板,因此可對8×8個無線通道進行衰減。

圖3展示了可編程衰減器的8×8結(jié)構(gòu)。本衰減器可對任一路無線信道模擬其它無線信道對其的影響。通過調(diào)節(jié)其它信道與該信道之間的衰減值,就可在實驗室模擬復(fù)雜的外場環(huán)境。

邏輯設(shè)計

可編程衰減器的核心技術(shù)在于其邏輯設(shè)計上。可編程衰減器的邏輯結(jié)構(gòu)根據(jù)其功能分為兩部分:實時衰減控制和靜態(tài)場景回放。

實時衰減控制

實時衰減控制模式是指用戶實時通過CPU下發(fā)各個通道之間的衰減值來控制不同無線信道的衰減,衰減值一旦下發(fā),相應(yīng)的無線信道的衰減器就會立即生效。

CPU與FPGA之間采用LOCALBUS進行通信。在FPGA中對0~7個IO板接口分配不同的地址,控制譯碼/通道選擇模塊通過LOCALBUS的地址線來選擇對應(yīng)的IO板;每個衰減器需要8bit的衰減量,3bit的通道編碼,因此LOCALBUS數(shù)據(jù)線上共有11bit有效數(shù)據(jù)。

譯碼模塊將這11bit數(shù)據(jù)中3bit的通道編碼譯碼成對應(yīng)的通道,將8bit的衰減值下發(fā)到對應(yīng)通道的數(shù)控衰減器上。

靜態(tài)場景回放

靜態(tài)場景回放是用戶將某個外場環(huán)境下各個無線信道的動態(tài)衰減參數(shù)記錄下來,記錄時間可長達數(shù)周。將這些數(shù)據(jù)下發(fā)給可編程衰減器即可在實驗室內(nèi)長時間模擬各類復(fù)雜的外場環(huán)境。

在該場景下,LOCALBUS的數(shù)據(jù)線除傳輸衰減值外還要傳32bit的時間數(shù)據(jù),每一bit代表1ms的時間,32bit就可支持最長7周的場景回放。

FPGA首先將32Mbit的DDRA寫滿數(shù)據(jù),然后定時控制自動啟動,從DDRA中讀取定時數(shù)據(jù)和衰減值,將定時數(shù)據(jù)提供給定時器。

當(dāng)定時器計時到定時數(shù)據(jù)代表的時間點時將該時刻的衰減值下發(fā)到對應(yīng)通道的衰減器上,實現(xiàn)無線信道衰減隨時間動態(tài)變化的場景;同時FPGA繼續(xù)將CPU下發(fā)的數(shù)據(jù)寫到DDRB中。當(dāng)DDRB充滿后,CPU暫停下發(fā)數(shù)據(jù),直到DDRA數(shù)據(jù)讀取完畢,此時FPGA切換到讀取DDRB的數(shù)據(jù),繼續(xù)向DDRA寫入新的數(shù)據(jù)。

FPGA外掛的兩個DDR構(gòu)成乒乓結(jié)構(gòu),使可編程衰減器能實現(xiàn)長時間不間斷的場景回放。

測試結(jié)果

該可編程衰減器的主要性能指標(biāo)如表1:

表1可編程衰減器主要參數(shù)的測試結(jié)果

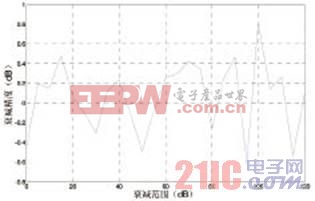

圖7展示了可編程衰減器單通道在衰減范圍內(nèi)的衰減精度。從圖中可以看到,在0~80dB的衰減范圍內(nèi)衰減精度可以達到0.5dB;在80dB~120dB衰減范圍內(nèi)衰減精度達到1dB。

圖7可編程衰減器衰減范圍內(nèi)的衰減精度

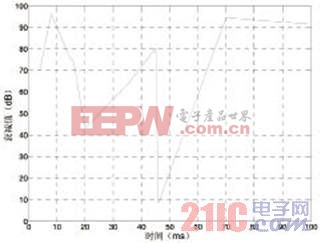

圖8展示了靜態(tài)場景回放的某一個時間段內(nèi)可編程衰減器一個無線信道內(nèi)衰減變化。在該模式下本衰減器可在1ms的時間間隔內(nèi)實現(xiàn)0~120dB的衰減跳變。

圖8靜態(tài)場景回放

結(jié)論

本文介紹了一種衰減范圍可達120dB,衰減精度為0.5dB的可編程衰減器設(shè)計。該衰減器可在實驗室環(huán)境中實現(xiàn)復(fù)雜的外場環(huán)境,可大大節(jié)省終端設(shè)備測試的成本和時間。

更多資訊請關(guān)注:21ic模擬頻道

評論