開關電容ADC及其驅動放大器之間的阻抗諧振匹配方法

高采樣速率模數轉換器(ADC)通常用在現代無線接收器設計中,以中頻(IF)采樣速率采集復數調制的信號。這類設計通常都選用基于CMOS開關電容的ADC,因為它們的低成本和低功耗特點很吸引人。但這類ADC采用一種直接連接到采樣網絡的無緩沖器的前端,這樣就會出現驅動ADC的放大器的輸入跟蹤和保持阻抗隨時間變化的問題。為了有效地驅動ADC,使噪聲最低和有用信號失真最小,必須設計一種無源網絡接口幫助抑制寬帶噪聲,并對跟蹤阻抗和保持阻抗進行變換以便為驅動放大器提供更好的負載阻抗。針對幾種常見的IF頻率,本文中提出了一種諧振匹配方法,用于將跟蹤和保持阻抗轉換為比較容易計算的負載,從而實現抗鋸齒濾波器的精密設計。

本文引用地址:http://www.104case.com/article/186344.htm開關電容ADC

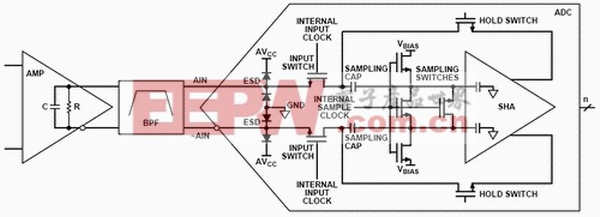

開關電容ADC不帶緩沖器,以便能降低功耗。這種ADC的采樣保持放大器電路(SHA)主要包括一個輸入開關、一個輸入采樣電容器、一個采樣開關和一個放大器。如圖1所示,輸入開關直接連接驅動器和采樣電容器。輸入開關閉合時(跟蹤模式),驅動器電路驅動輸入電容器,當此模式結束時,輸入電容器開始對輸入信號進行采樣(捕獲)。而當輸入開關斷開時(保持模式),驅動器被輸入電容器隔離。ADC的跟蹤模式周期和保持模式周期大約相等。

圖1 連接到放大器驅動器的開關電容ADC簡化輸入模型

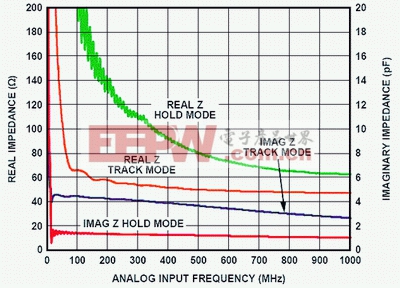

圖2 AD9236在跟蹤和保持兩種模式下的不同輸入頻率

在SHA的跟蹤模式期間和保持模式期間,ADC輸入阻抗的狀態是不同的,這就很難使ADC的輸入阻抗與驅動電路之間始終匹配。因為ADC只能在跟蹤模式期間檢測輸入信號,所以在此期間輸入阻抗應與驅動電路匹配。輸入阻抗與頻率的關系主要由采樣電容器和信號通路中所有的寄生電容決定。為了精確地匹配阻抗,了解輸入阻抗和頻率的關系是非常必要的。圖2為AD9236在輸入頻率高達1GHz時的輸入阻抗特性。

藍色曲線和紅色曲線分別表示ADC輸入SHA網絡在跟蹤和保持模式下輸入電容阻抗的虛部(對應右邊的縱坐標)。在小于100 MHz時,電容阻抗的虛部從跟蹤模式下的大于4pF變化到保持模式下的1pF。輸入SHA網絡在跟蹤和保持模式下的輸入阻抗實部分別用橙色和綠色曲線表示(對應左邊的縱坐標)。正如預期的那樣,與保持模式相比,跟蹤模式下的阻抗值要低得多。帶緩沖器輸入的ADC阻抗在整個標稱寬帶內都保持恒定,而開關電容ADC的輸入阻抗在最初的100MHz輸入帶寬內會產生很大變化。

阻抗諧振匹配方法

為了有效地將有用信號耦合到ADC的理想奈奎斯特(Nyquist)區內,必須要徹底了解ADC在有用頻率范圍內的跟蹤和保持阻抗。有幾家ADC制造商已經提供了供網絡分析使用的散射參數和(或)阻抗參數。輸入阻抗數據可用于設計阻抗變換網絡,其有助于捕獲有用信號并抑制其他頻率范圍內的無用信號。

如果知道了任何輸入系統的差分輸入阻抗,那么有可能設計出一個具有低信號損耗的電抗匹配網絡。輸入阻抗可以用復數ZIN=R+jX表示,其中R表示輸入阻抗中的等效串聯電抗,X表示虛串聯電抗,這樣就可以找到一個將這種復數阻抗變換成負載的等效網絡。通常,輸入阻抗被等效成一個并聯RC網絡。為了找到一個等效的RC并聯網絡,我們可以利用下述公式將阻抗轉換為導納。![]() (1)

(1)

有許多軟件程序可以計算復數的倒數,例如Matlab和MathCad,甚至像Excel的較新版本都有此功能。

IF采樣和奈奎斯特區考慮

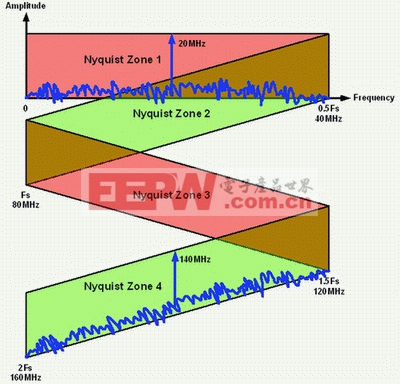

只有當有用信號或頻率處于第一奈奎斯特區內時才會進行基帶采樣。但是,有些轉換器可以在高于第一奈奎斯特區的頻域內采樣,這被稱作欠采樣或是IF采樣。圖3示出如何用相對于80 MHz采樣頻率(Fs)的140 MHz中頻來定義ADC的奈奎斯特區,信號實質上處于第四奈奎斯特區內。IF頻率的鏡像頻率可以映射到第一奈奎斯特區,這就好像在第一奈奎斯特區看到一個20 MHz的信號一樣。還應該注意到大多數FFT分析儀,例如ADC AnalyzerTM,只能分析第一奈奎斯特區或0~0.5Fs的FFT。因此,如果有用頻率高于0.5Fs,那么鏡像頻率可被映射到第一奈奎斯特區或者常說的基帶。如果雜散頻率也在可用帶寬內,這樣就會使事情變得復雜。

圖3 奈奎斯特區的定義

那么,當ADC偏離采樣頻率0.5Fs時怎能滿足奈奎斯特準則呢?這里重述Walt Kester在ADI高速IC研討會技術資料中介紹的“奈奎斯特準則”,即信號的采樣速率必須大于等于其帶寬的兩倍,才能保持信號的完整信息,該準則也可見式(2)。

FS>2FBW (2)

其中,Fs表示采樣頻率,FBW表示最高有用頻率。 這里的關鍵是要注意有用頻率的位置。只要信號沒有重疊并且留在一個奈奎斯特區內,就可以滿足奈奎斯特準則。唯一不同的是有用頻率的位置從第一奈奎斯特區到了高階奈奎斯特區。

IF采樣已經越來越受歡迎,因為它允許設計工程師去除信號鏈中的混頻級電路。這樣就能提高性能,因為減少了信號鏈中元件總數量,實際上降低了引入系統的附加噪聲,從而進一步提高系統總的信噪比(SNR)。在某些情況下,這樣做還可以提高無雜散動態范圍性能(SFDR),因為消除了混頻級電路會降低本地振蕩器(LO)通過混頻器引起的泄漏。

在進行IF采樣時,對高頻抗鋸齒濾波器(AAF)的設計是相當重要的。在大多數情況下,AAF被設計在有用頻帶內的中心。在IF采樣應用中,恰當的濾波器設計是至關重要的,以便低奈奎斯特區內的低頻噪聲不會落入有用頻率所在的高階奈奎斯特區。而且,不良的濾波器設計會導致在本底噪聲的基帶鏡像出現過多的噪聲。圖4顯示了抗鋸齒濾波器的阻帶衰減特性。

很顯然,系統動態范圍和帶通濾波器的階數有直接的關系。此外,系統的階數還依賴于系統的分辨率。分辨率越低,本底噪聲就越高,信號具有的混頻效應就越小,因此對系統的階數要求就越低。但是,有些高階濾波器可能會在通帶中產生較多的紋波,這會對系統的性能起到反作用,因為其引發了相位失真和幅度失真。總之,在設計抗鋸齒濾波器時必須非常小心。

電容相關文章:電容原理 電容傳感器相關文章:電容傳感器原理

評論