VGA視頻分配器系統的信號完整性及改善措施

抑制接地反彈本文引用地址:http://www.104case.com/article/186039.htm

要抑制接地反彈的影響,首先是減少IC封裝的分布電感。其次,是采用分布電感較小的IC封裝技術,表面貼片式封裝通常比DIP封裝的接地反彈低30%。然后是降低印刷電路板端的分布電感量。由于電感與導體的長度成正比,與寬度成反比,所以在高速數字系統中容易出現反彈。可以在里層擺放一個或一個以上的接地層,且接地層面積寬廣,可以減少其地端回路的電感量。另外,電路設計時應盡可能避免讓某個邏輯門驅動太多的負載。因為在數字電路中,若有多個并聯的邏輯裝置,總輸入電容是每個邏輯裝置的輸入電容之和。

視頻分配器信號完整性分析

當把一路輸出視頻信號提供給多臺視頻設備使用時,就要考慮使用VGA視頻分配器。其實現方式主要有:晶體管放大驅動多路輸出和集成芯片視頻分配器兩種。由于前者電源電壓低,電路的動態范圍小,且高頻衰減較大,只能用在對這兩方面要求不高的場合。因此,為使所設計的分配器能夠實現高保真傳輸,本文采用集成芯片作為視頻驅動。

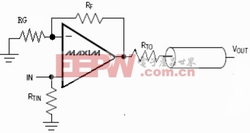

采用15針VGA母插頭作為視頻信號輸入輸出接口,信號經過VGA插頭后,分為行、場及R、G、B信號分別輸出。行、場信號經過晶體管放大至輸出端,R、G、B信號經集成芯片MAX4020視頻放大器驅動和終端濾波網絡濾波后送至輸出端,如圖2所示。

MAX4020是單位增益放大器,+5V電源驅動,輸出電流可達120mA。在VGA 分配器的設計中,信號完整性最突出的問題就是阻抗匹配。理想傳輸線L被內阻為R0的數字信號驅動源Vs驅動,傳輸線的特性阻抗為Z0,負載阻抗為RL,如圖3所示。如果終端阻抗(B點)跟傳輸線阻抗(A點)不匹配,就會形成反射,反射回來的電壓幅值由負載反射系數ρL決定。ρL可由下式得出:

ρL=(RL-Z0)/(RL+Z0)

從終端反射回的電壓到達源端時,可再次反射回負載端,形成二次反射,此時反射電壓的幅值由源反射系數ρs決定,ρs可由下式得出:

ρs=(R0-Z0)/(R0+Z0)

由上式可知,只要匹配電路的設計滿足源端阻抗R0等于傳輸線的特性阻抗Z0,或者負載阻抗RL等于傳輸線的特性阻抗Z0即可。

在實際的電路設計中一般都采用源端阻抗等于負載端阻抗的端接匹配方式 ,在負載端加入一下拉到地的電阻來實現匹配。由于系統負載阻抗為75Ω, 芯片輸出電阻為8Ω,因此,只要在源端串連一個67Ω的匹配電阻RTO即可。所插入的串行電阻阻值加上驅動源的輸出阻抗應大于等于傳輸線阻抗(輕微過阻尼)。這種匹配方式使源端反射系數為零,從而抑制了從負載反射回來的信號。其優點在于:每條線只需要一個端接電阻,無需與電源相連接,消耗功率小。實際調試中得到的圖像無重影、雪花,但稍有偏暗。原因是采用此端接方式,源端匹配電阻在輸出電路中分壓,從而導致圖像顯示偏暗。

對電路做如圖4所示的配置:在反饋端加一個接地電阻RG,從而放大電路的驅動電壓。設計當中要注意反饋電阻RF和輸入電阻RG的阻值選擇要符合系統配置。阻值過大會增加電壓噪聲,影響放大器的輸入容量,從而產生不必要的零極點,降低帶寬甚至產生振蕩。調試結果:圖像顯示與輸入相同。

仿真分析

在現代高速電路設計中,仿真分析工具能夠給設計者反饋準確、直觀的設計結果,便于提早發現隱患,及時修改,縮短設計時間,降低設計成本。

圖4 MAX4020配置原理圖

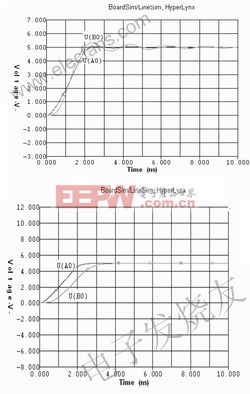

圖5 Hyperlynx仿真結果

BoardSim是HyperLynx公司開發的仿真工具。BoardSim用于布線以后快速地分析設計中的信號完整性、電磁兼容性和串擾問題,生成串擾強度報告,區分并解決串擾問題。電路在沒有進行阻抗匹配以及進行阻抗匹配后的仿真結果如圖5所示。可以看到,沒有進行阻抗匹配的電路示波器中接收端的電壓波形有很大的過沖和下沖,這樣在接收端IC 每個周期將會收到一個非常陡的時鐘信號,而且這樣的波形將會引起很強的電磁輻射。而進行匹配的電路經仿真發現信號完整性問題得到了很好的解決。

結語

本文分析了高速電路設計中的信號完整性問題,提出了改善信號完整性的一些措施,并結合一個VGA視頻分配器系統的設計過程,具體分析了改善信號完整性的方法。實踐證明,正確的電路設計結合合理的建模仿真是解決高速系統設計中信號完整性問題的有效措施。

評論