基于簡(jiǎn)單的FIFO提供數(shù)據(jù)寬度轉(zhuǎn)換

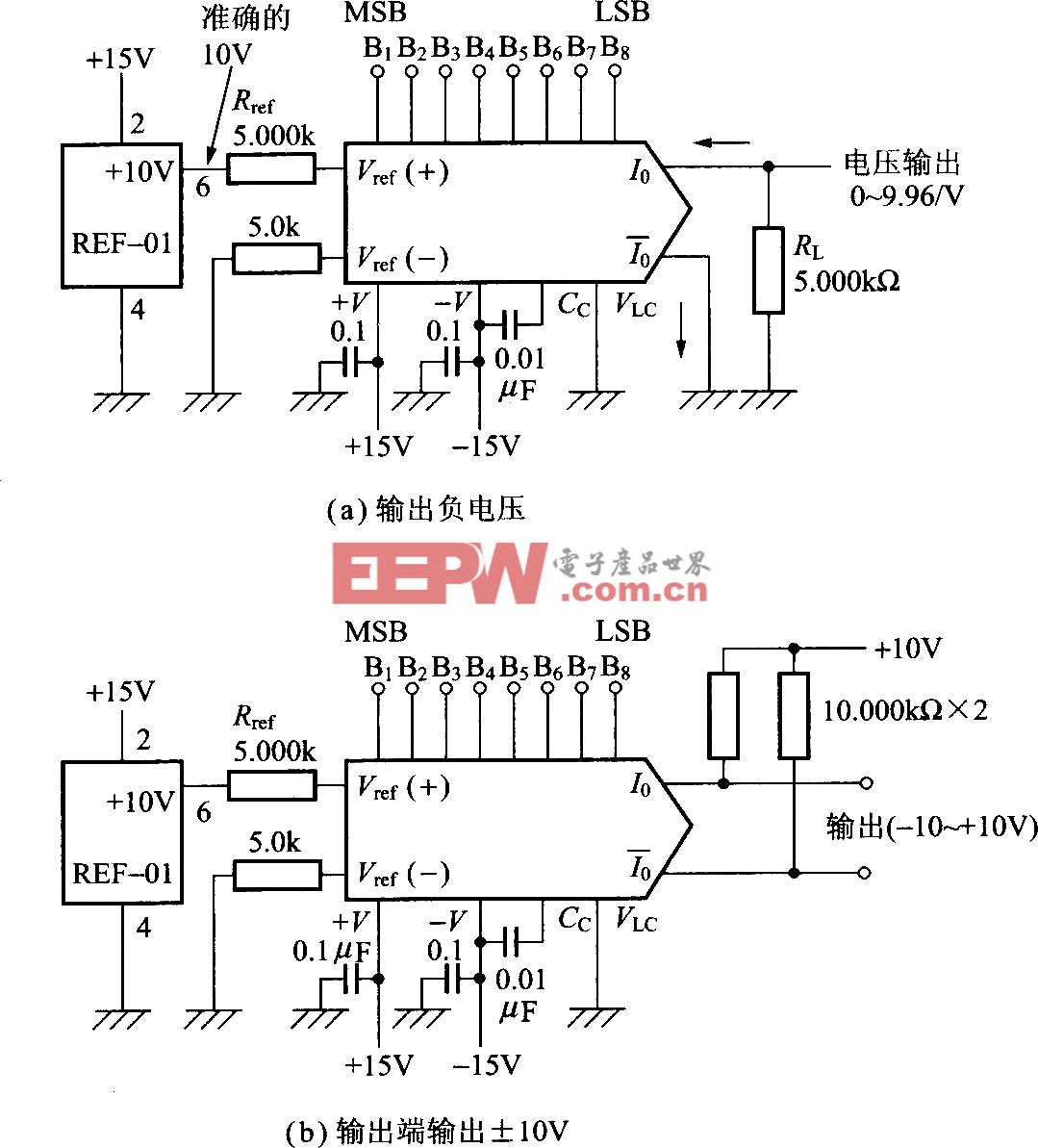

許多設(shè)計(jì)需要FIFO彈性緩沖器,在不同時(shí)鐘速率的次系統(tǒng)和通道的需求中形成橋梁。然而,在某些應(yīng)用中,需要FIFO緩沖器實(shí)現(xiàn)數(shù)據(jù)轉(zhuǎn)換。一個(gè)例子是,通過(guò)FIFO緩沖器,將8位ADC連接到16位數(shù)據(jù)總線的微處理器(圖1)。不幸地,大部分普遍使用的FIFO緩沖器不適于這個(gè)應(yīng)用。本設(shè)計(jì)方案描述了為不同寬度讀寫數(shù)據(jù)端口的數(shù)據(jù)寬度轉(zhuǎn)換,怎樣基于FPGA的FIFO實(shí)現(xiàn)共有時(shí)鐘(同步)。可以使用Xilinx的Spartan II系列FPGA實(shí)現(xiàn)這種FIFO。這個(gè)方法使用了片上DLL(延遲鎖相環(huán))宏、分布式存儲(chǔ)器和簡(jiǎn)單的計(jì)數(shù)器邏輯(圖2)。

本文引用地址:http://www.104case.com/article/186034.htm

FIFO輸入數(shù)據(jù)的寬度為8位;然而,輸出數(shù)據(jù)的寬度為16位。在讀寫動(dòng)作中只使用一個(gè)共有時(shí)鐘。關(guān)鍵是為了使用時(shí)鐘DLL,它不只是最小化時(shí)鐘脈沖相位差,還提供雙倍輸出的時(shí)鐘頻率。所以,可以實(shí)現(xiàn)輸入數(shù)據(jù)的雙重?cái)?shù)據(jù)率,write_data_in。通過(guò)監(jiān)測(cè)DLL輸出時(shí)鐘的樣本,DLL可以補(bǔ)償走線網(wǎng)絡(luò)的延遲,有效地消除外部輸入端口到設(shè)備中單獨(dú)時(shí)鐘負(fù)載的延遲。替代使用的阻塞存儲(chǔ)器,本設(shè)計(jì)在FIFO中使用分布式存儲(chǔ)器保存數(shù)據(jù)。實(shí)際上,選擇阻塞存儲(chǔ)器還是分布式存儲(chǔ)器,依靠系統(tǒng)中FIFO的重要性。如果不是很關(guān)鍵,可以考慮使用分布式存儲(chǔ)器。

存儲(chǔ)器可以放在FPGA的任何位置。如果堅(jiān)持使用阻塞存儲(chǔ)器,可以簡(jiǎn)單的改變VHDL代碼。可只使用一些RAM宏來(lái)替代分布式存儲(chǔ)器。點(diǎn)擊下載FIFO 的VHDL代碼。FIFO一般使用Gray代碼計(jì)數(shù)器或線性反饋移位寄存器作為讀或?qū)懹?jì)數(shù)器。為實(shí)現(xiàn)邏輯大小的最小化,本設(shè)計(jì)只使用兩個(gè)從0到7的整數(shù)和帶進(jìn)位的計(jì)數(shù)器。當(dāng)讀和寫計(jì)數(shù)器相等,且進(jìn)位為0時(shí),F(xiàn)IFO為空。當(dāng)寫計(jì)數(shù)器加1等于讀計(jì)數(shù)器,且進(jìn)位為1時(shí),F(xiàn)IFO為滿。

更多資訊請(qǐng)關(guān)注:21ic模擬頻道

存儲(chǔ)器相關(guān)文章:存儲(chǔ)器原理

塵埃粒子計(jì)數(shù)器相關(guān)文章:塵埃粒子計(jì)數(shù)器原理 鎖相環(huán)相關(guān)文章:鎖相環(huán)原理

評(píng)論