0.35μmCMOS光接收機(jī)前置放大器設(shè)計(jì)

4 模擬結(jié)果

采用臺(tái)灣TSMC0.35μmCMOS工藝提供的BSIM3元件模型和商用的SmartSpice電路仿真軟件對(duì)前置放大器進(jìn)行了仿真。

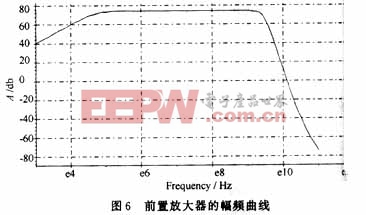

模擬交流分析得到的幅頻特性曲線如圖6所示。放大器總的增益為73 dBΩ,3 dB帶寬為2.2 GHz。低頻截止頻率為50 kHz。

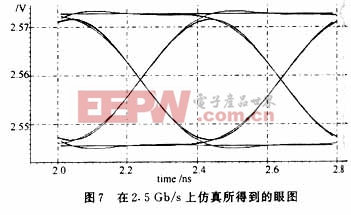

圖7為輸入5μA,2.5 Gb/s的偽隨機(jī)序列,采用SmartSpice分析所得輸出眼圖。

5 版圖設(shè)計(jì)

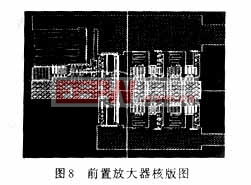

前置放大器核版圖如圖8所示,圖中左上部分為跨阻放大器,是一個(gè)不對(duì)稱的圖形。右半部分是兩級(jí)差分放大器,由于是對(duì)稱的圖形,所以在繪制版圖時(shí)可以只畫上邊部分,然后復(fù)制翻轉(zhuǎn)下來。跨阻放大器和差分放大器之間是RC低通網(wǎng)絡(luò)的電阻,電容值比較大,采用外接形式。上下邊界處圖形為電源線,線的寬度要足夠?qū)挘悦怆娏鬟^大燒毀。中間橫線為地線,同時(shí)使用兩層金屬,這樣既減小了線寬、節(jié)省了面積又能保證通過大的電流。

該版圖采用Cadence設(shè)計(jì)工具設(shè)計(jì)。面積為40.15 mm×0.20 mm。該芯片已通過臺(tái)灣TSMC0.35μm的N阱、兩層多晶硅、四層金屬的CMOS工藝流片,由于前置放大器和主放大器一同流片,芯片總面積為1 mm×0.70 mm。

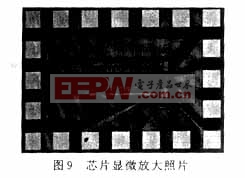

芯片顯微放大照片如圖9所示,圖中左半部分為前置放大電路,右半部分為限幅放大電路。

6 結(jié)果測(cè)試

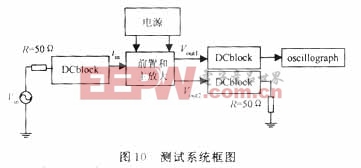

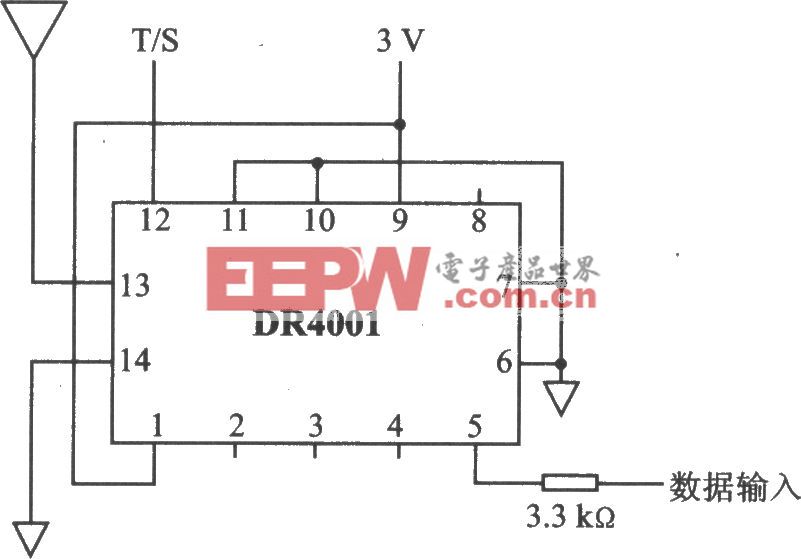

由于測(cè)試條件所限,測(cè)試中只能用偽隨機(jī)碼發(fā)生器產(chǎn)生的電壓脈沖信號(hào)來代替高速的脈沖電流信號(hào),測(cè)試系統(tǒng)框圖如圖10所示。

圖11為整個(gè)芯片在片測(cè)試結(jié)果。前置放大器輸入為2.5 Gb/s峰峰值10 mV的電壓信號(hào),主放大器輸出擺幅為200 mVp-p。

輸出數(shù)據(jù)的眼圖中心上偏約60 mV,這是因?yàn)闇y(cè)試采用單端輸出。雙端輸出時(shí)無此現(xiàn)象。

7 結(jié) 語

本文介紹了采用0.35μmCMOS工藝實(shí)現(xiàn)用于SDH系統(tǒng)STM-16速率級(jí)光接收機(jī)的前置放大器的設(shè)計(jì)。電路模擬結(jié)果和對(duì)芯片測(cè)試結(jié)果令人滿意,準(zhǔn)備做印刷電路板對(duì)其進(jìn)一步測(cè)試,并進(jìn)行優(yōu)化改進(jìn)。

評(píng)論