針對DDR2-800和DDR3的PCB信號完整性設計

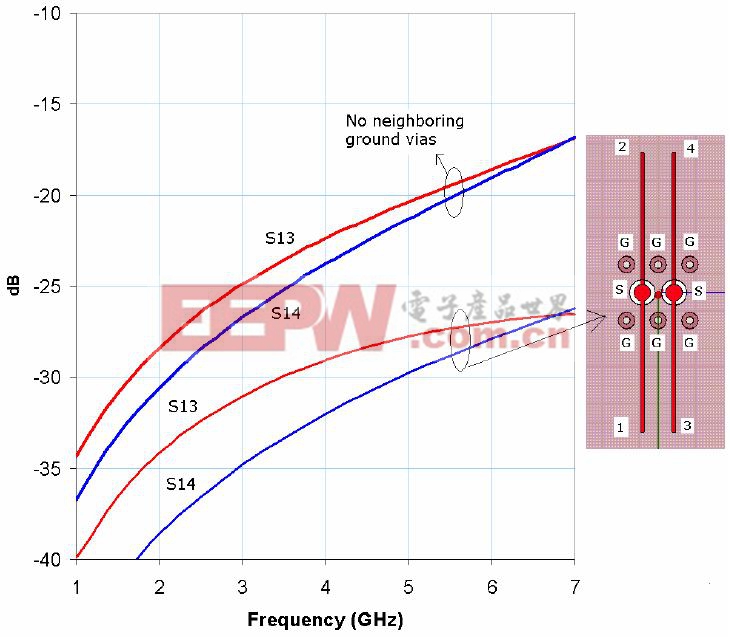

圖8: 相互耦合走線的s-parameters

6. 電源完整性

這里的電源完整性指的是在最大的信號切換情況下,其電源的容差性。當未符合此容差要求時,將會導致很多的問題,比如加大時鐘抖動、數據抖動和串擾。

這里,可以很好的理解與去偶相關的理論,現在從”目標阻抗”的公式定義開始討論。

Ztarget=Voltage tolerance/Transient Current (1)

在這里,關鍵是要去理解在最差的切換情況下瞬間電流(Transient Current)的影響,另一個重要因素是切換的頻率。在所有的頻率范圍里,去耦網絡必須確保它的阻抗等于或小于目標阻抗(Ztarget)。在一塊 PCB上,由電源和地層所構成的電容,以及所有的去耦電容,必須能夠確保在100KHz左右到100-200MH左右之間的去耦作用。頻率在 100KHz以下,在電壓調節模塊里的大電容可以很好的進行去耦。而頻率在200MHz以上的,則應該由片上電容或專用的封裝好的電容進行去耦。實際的電源完整性是相當復雜的,其中要考慮到IC的封裝、仿真信號的切換頻率和PCB耗電網絡。對于PCB設計來說,目標阻抗的去耦設計是相對來說比較簡單的,也是比較實際的解決方案。

在 DDR的設計上有三類電源,它們是VDD、VTT和Vref。VDD的容差要求是5%,而其瞬間電流從Idd2到Idd7大小不同,詳細在JEDEC里有敘述。通過電源層的平面電容和專用的一定數量的去耦電容,可以做到電源完整性,其中去耦電容從10nF到10uF大小不同,共有10個左右。另外,表貼電容最合適,它具有更小的焊接阻抗。

Vref要求更加嚴格的容差性,但是它承載著比較小的電流。顯然,它只需要很窄的走線,且通過一兩個去耦電容就可以達到目標阻抗的要求。由于Vref相當重要,所以去耦電容的擺放盡量靠近器件的管腳。

然而,對VTT的布線是具有相當大的挑戰性,因為它不只要有嚴格的容差性,而且還有很大的瞬間電流,不過此電流的大小可以很容易的就計算出來。最終,可以通過增加去耦電容來實現它的目標阻抗匹配。

在4層板的PCB里,層之間的間距比較大,從而失去其電源層間的電容優勢,所以,去耦電容的數量將大大增加,尤其是小于10 nF的高頻電容。詳細的計算和仿真可以通過EDA工具來實現。

7. 時序分析

對于時序的計算和分析在一些相關文獻里有詳細的介紹,下面列出需要設置和分析的8個方面:

1. 寫建立分析: DQ vs. DQS

2. 寫保持分析: DQ vs. DQS

3. 讀建立分析: DQ vs. DQS

4. 讀保持分析: DQ vs. DQS

5. 寫建立分析: DQS vs. CLK

6. 寫保持分析: DQS vs. CLK

7. 寫建立分析: ADDR/CMD/CNTRL vs. CLK

8. 寫保持分析: ADDR/CMD/CNTRL vs. CLK

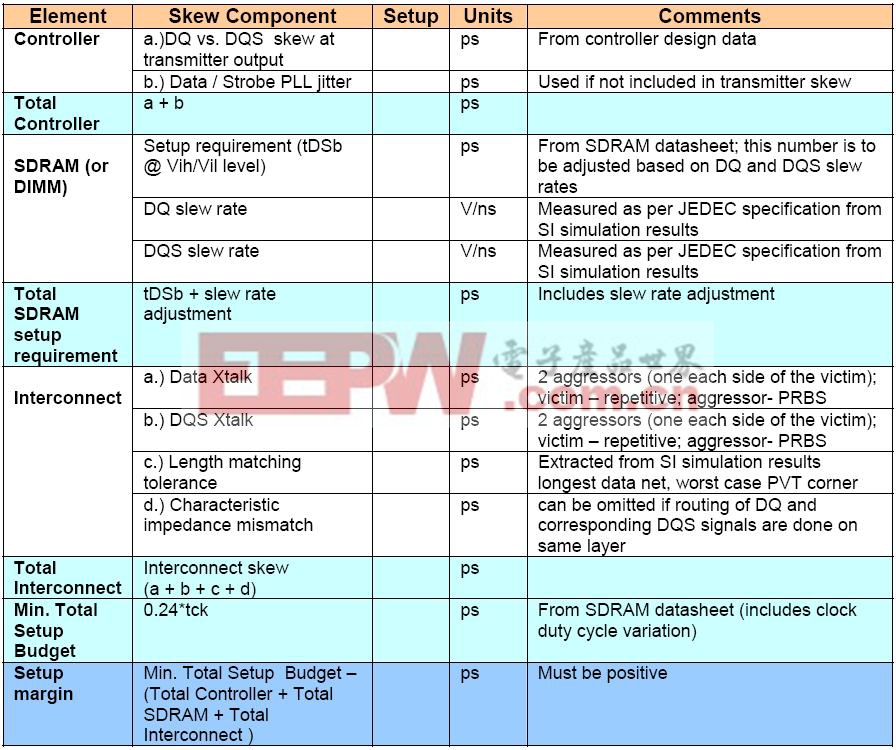

表2舉了一個針對寫建立(Write Setup)分析的例子。表中的一些數據需要從控制器和存儲器廠家獲取,段”Interconnect”的數據是取之于SI仿真工具。對于DDR2上面所有的8 項都是需要分析的,而對于DDR3,5項和6項不需要考慮。在PCB設計時,長度方面的容差必須要保證total margin是正的。

表2: 針對DQ vs. DQS的DDR3寫保持時域分析案例

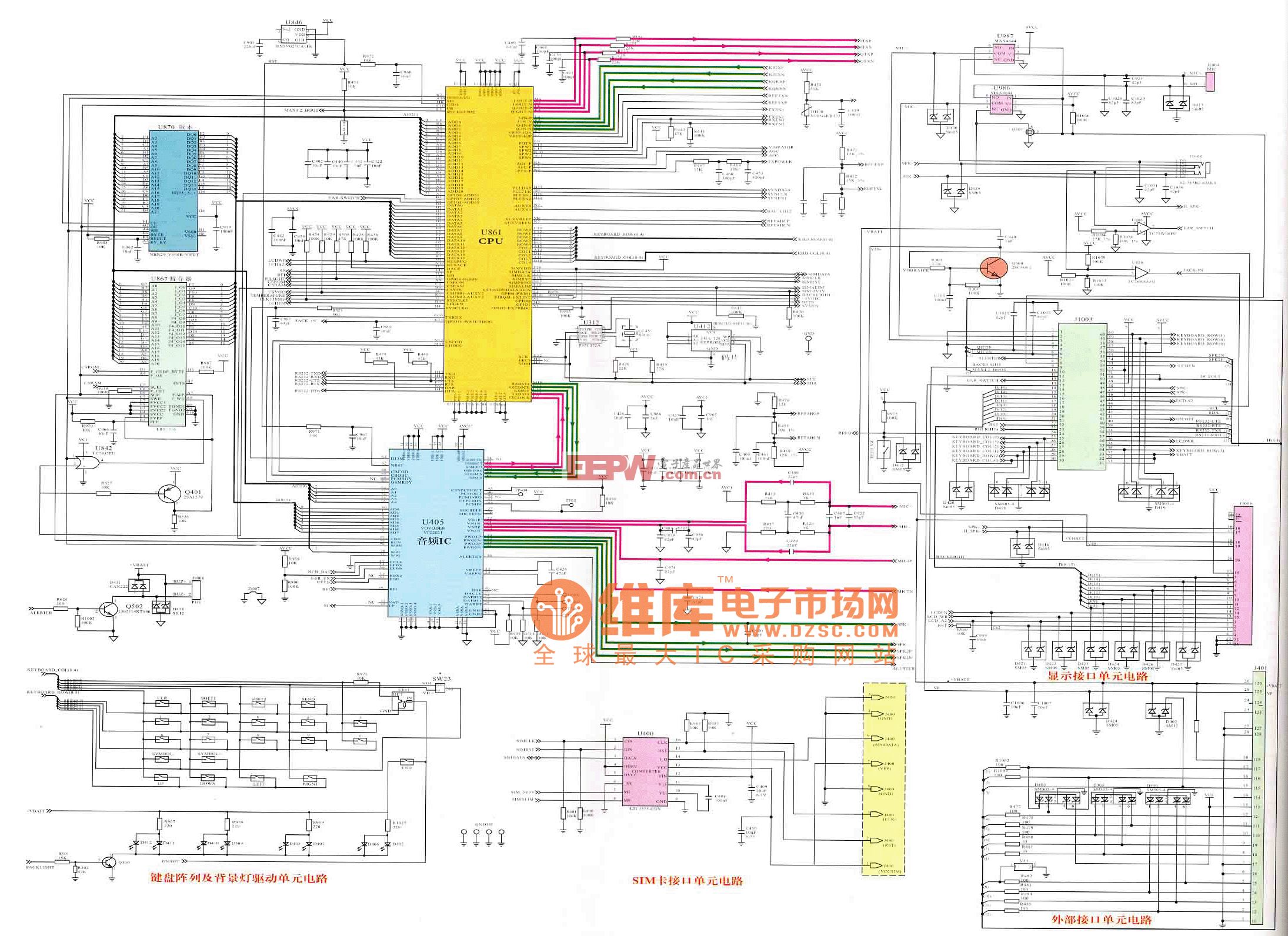

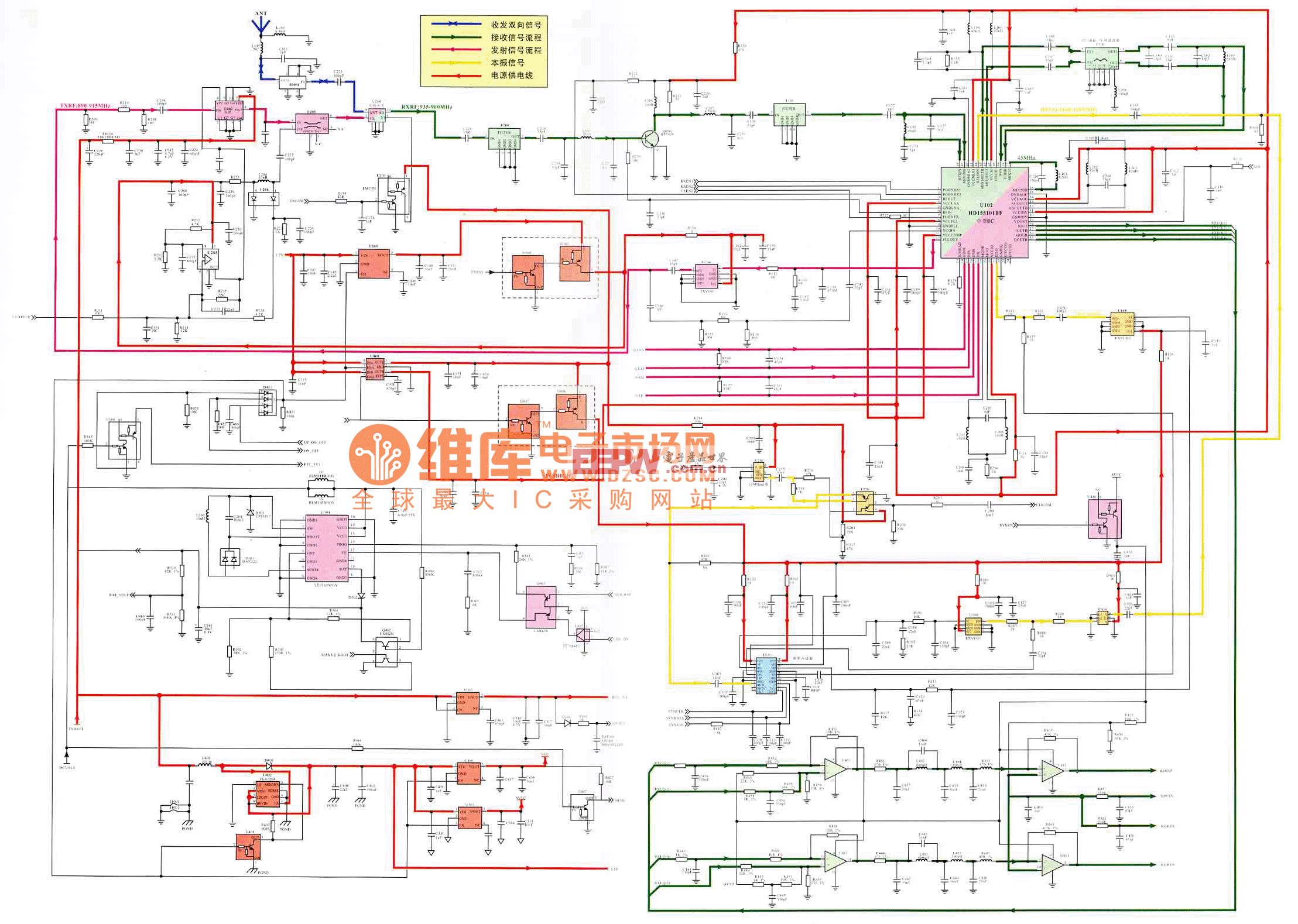

8. PCB Layout

在實際的PCB設計時,考慮到SI的要求,往往有很多的折中方案。通常,需要優先考慮對于那些對信號的完整性要求比較高的。畫PCB時,當考慮一下的一些相關因素,那么對于設計PCB來說可靠性就會更高。

1. 首先,要在相關的EDA工具里要設置好里設置好拓撲結構和相關約束。

2. 將BGA引腳突圍,將ADDR/CMD/CNTRL引腳布置在DQ/DQS/DM字節組的中間,由于所有這些分組操作,為了盡可能少的信號交叉,一些獨立的管腳也許會被交換到其它區域布線。

3. 由串擾仿真的結果可知,盡量減少短線(stubs)長度。通常,短線(stubs)是可以被削減的,但不是所有的管腳都做得到的。在BGA焊盤和存儲器焊盤之間也許只需要兩段的走線就可以實現了,但是此走線必須要很細,那么就提高了PCB的制作成本,而且,不是所有的走線都只需要兩段的,除非使用微小的過孔和盤中孔的技術。最終,考慮到信號完整性的容差和成本,可能選擇折中的方案。

4. 將Vref的去耦電容靠近Vref管腳擺放;Vtt的去耦電容擺放在最遠的一個SDRAM外端;VDD的去耦電容需要靠近器件擺放。小電容值的去耦電容需要更靠近器件擺放。正確的去耦設計中,并不是所有的去耦電容都是靠近器件擺放的。所有的去耦電容的管腳都需要扇出后走線,這樣可以減少阻抗,通常,兩端段的扇出走線會垂直于電容布線。

5. 當切換平面層時,盡量做到長度匹配和加入一些地過孔,這些事先應該在EDA工具里進行很好的仿真。通常,在時域分析來看,差分線里的兩根線的要做到延時匹配,保證其誤差在+/- 2ps,而其它的信號要做到+/- 10 ps。

9. DIMM

之前介紹的大部分規則都適合于在PCB上含有一個或更多的DIMM,唯一列外的是在DIMM里所要考慮到去耦因素同在DIMM組里有所區別。在DIMM組里,對于ADDR/CMD/CNTRL所采用的拓撲結構里,帶有少的短線菊花鏈拓撲結構和樹形拓撲結構是適用的。

10. 案例

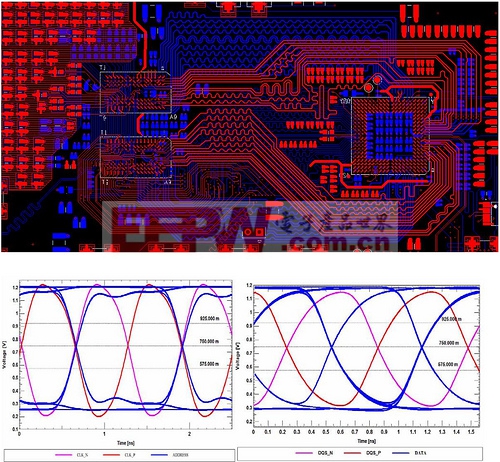

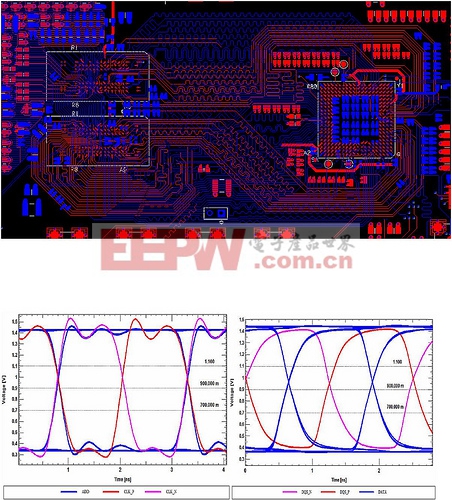

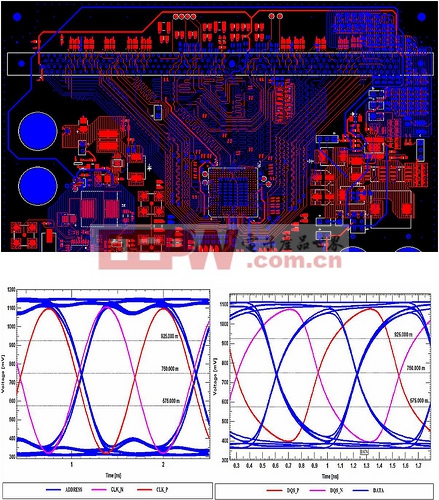

上面所介紹的相關規則,在DDR2 PCB、DDR3 PCB和DDR3-DIMM PCB里,都已經得到普遍的應用。在下面的案例中,我們采用MOSAID公司的控制器,它提供了對DDR2和DDR3的操作功能。在SI仿真方面,采用了 IBIS模型,其存儲器的模型來自MICRON Technolgy,Inc,對于DDR3 SDRAM的模型提供了1333 Mbps的速率。在這里,數據是操作是在1600 Mbps下的。對于不帶緩存(unbuffered)的DIMM(MT_DDR3_0542cc)EBD模型是來自Micron Technology,下面所有的波形都是采用通常的測試方法,且是在SDRAM die級進行計算和仿真的。圖2所示的6層板里,只在TOP和BOTTOM層進行了布線,存儲器由兩片的SDRAM以菊花鏈的方式所構成。而在DIMM的案例里,只有一個不帶緩存的DIMM被使用。圖9-11是對TOP/BOTTOM層布線的一個閃照圖和信號完整性仿真圖。

圖9: 只有在TOP和BOTTOM層走線的DDR3的仿真波形

(左邊的是ADDRESS和CLOCK網絡,右邊的是DATA和DQS網絡,其時鐘頻率在800 MHz,數據通信率為1600Mbps)

圖10: 只有在TOP和BOTTOM層走線的DDR2的仿真波形

(左邊的是ADDRESS和CLOCK網絡,右邊的是DATA和DQS網絡,其時鐘頻率在400 MHz,數據通信率為800Mbps)

圖11: 只有在TOP和BOTTOM層走線的DDR3-DIMM的仿真波形

(左邊的是ADDRESS和CLOCK網絡,右邊的是DATA和DQS網絡)

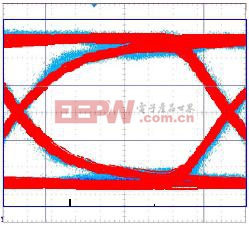

最好,圖12顯示了兩個經過比較過的數據信號眼圖,一個是仿真的結果,而另一個是實際測量的。在上面的所有案例里,波形的完整性的完美程度都是令人興奮的。

圖12: 800 Mbps DDR2的數據信號仿真眼圖(紅) 和 實測眼圖 (藍)

11. 結論

本文,針對DDR2/DDR3的設計,SI和PI的各種相關因素都做了全面的介紹。對于在4層板里設計800 Mbps的DDR2和DDR3是可行的,但是對于DDR3-1600 Mbps是具有很大的挑戰性。

模擬信號相關文章:什么是模擬信號

電容相關文章:電容原理 電容傳感器相關文章:電容傳感器原理 上拉電阻相關文章:上拉電阻原理

評論