在FPGA上建立MATLAB和Simulink算法原型

重用具有協同仿真功能的系統級測試平臺進行HDL驗證

功能驗證:HDL協同仿真使工程師能夠重用Simulink模型,將激勵驅動至HDL仿真器,并對仿真輸出執行交互式系統級分析(圖8)。

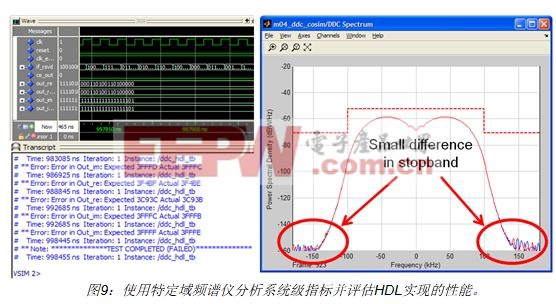

HDL仿真僅提供數字波形輸出,而HDL協同仿真則提供了顯示HDL代碼的完整視圖,并可以訪問Simulink的全套系統級分析工具。當工程師觀察到預期結果與HDL仿真結果存在差異時,可借助協同仿真進一步了解該失配所產生的系統級影響。

例如,在圖9中,頻譜儀視圖可以使工程師做出明智決定,忽略預期結果與HDL仿真結果之間的失配,其原因是該差異位于阻帶區。相比之下,數字波形輸出只是將預期結果與HDL仿真結果的失配標記為誤差。盡管工程師最終可能得出相同的結論,但這將需要更多的時間完成所需的分析。

測試覆蓋率:工程師可以使用HDL驗證工具、Simulink設計驗證工具和ModelSim/Questa自動執行代碼覆蓋率分析。在該工作流程中,Simulink設計驗證工具可針對模型覆蓋率生成一套測試用例。HDL驗證工具自動使用這一套測試用例運行ModelSim/Questa,收集代碼覆蓋率數據,以對生成的代碼加以全面分析。

使用FPGA在環仿真加速驗證

使用系統級仿真和HDL協同仿真驗證DDC算法之后,便可以立即在FPGA目標平臺上部署DDC算法。對算法執行基于FPGA的驗證(也稱為FPGA在環仿真)可以增強對算法在現實環境中有效運行的信心。相比基于主機的HDL仿真,該驗證可以使工程師更快地運行測試方案。

對于DDC算法而言,可以使用Simulink模型驅動FPGA輸入激勵并分析FPGA的輸出(圖10)。與HDL協同仿真一樣,在Simulink中始終可以利用相關數據進行分析。

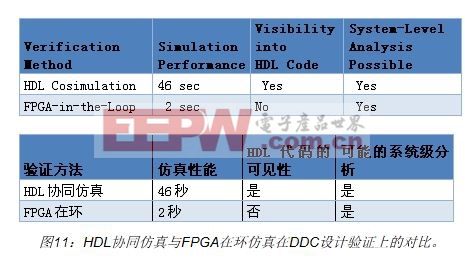

圖11對比了HDL協同仿真和FPGA在環仿真這兩種用于DDC設計的驗證方法。在本案例中,FPGA在環仿真的速度是HDL協同仿真的23倍。這樣的速度提升使工程師能夠運行更廣泛的測試用例并對其設計進行回歸測試。這使他們能夠識別出有待進一步分析的潛在問題區域。

盡管HDL協同仿真速度較慢,但它卻提高了HDL代碼的可見性。因此,它很適合針對FPGA在環仿真過程中發現的問題區域進行更詳細的分析。

本文小結

如果工程師遵循本文所述的四種最佳方法,開發FPGA原型將比傳統的手動工作流程快出許多,并能使工程師信心倍增。此外,工程師還可以在整個開發過程中繼續優化自己的模型,并快速地重新生成有關FPGA實現的代碼。與依賴手工編寫HDL的傳統工作流程相比,這種能力可以顯著縮短設計迭代的周期。

評論