基于Nios II的CCD采集系統(tǒng)的設計

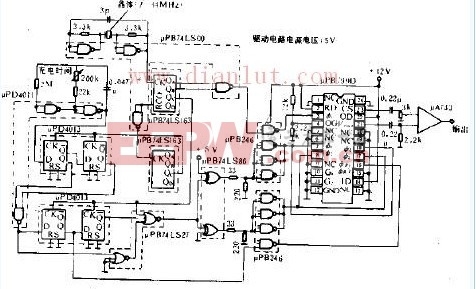

內部寄存器描述如表1所列。由于本系統(tǒng)中AD9844A工作于CCD模式,內部操作寄存器、VGA增益寄存器、箝位電壓寄存器及采樣增益寄存器的設置均為默認值。本設計所要做的是配置控制寄存器,選擇同步時鐘的極性,實現(xiàn)與時鐘發(fā)生器的時鐘同步,即采樣時鐘SHP/SHD為高電平觸發(fā)采樣周期,箝位時鐘CLP為低電平有效,數(shù)據(jù)輸出時鐘DATACLK為下降沿觸發(fā)。芯片內部寄存器的工作方式通過一個3線串口編程得到。本文引用地址:http://www.104case.com/article/185434.htm

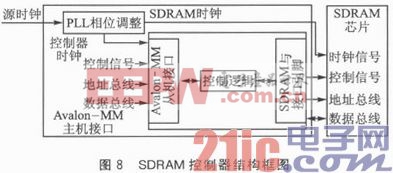

1.2.4 SDRAM模塊

Avalon總線接口的SDRAM控制器結構框圖如圖8所示。與FPGA片內的SDRAM控制器IP核與外部的SDRAM存儲器芯片之間的硬件接口,這些接口包括了SDRAM芯片的時鐘接口(clk)、時鐘屏蔽接口(cke)、地址總線(addr)、塊選信號(ba)、片選信號(cs)、行選信號(ras)、列選信號(can)、寫選通信號(we)、數(shù)據(jù)字節(jié)屏蔽信號(dqm)、數(shù)據(jù)總線(dq)。需要注意的是,PLL輸出連接到SDRAM芯片和SDRAM控制器IP核模塊工作的兩個時鐘是同頻不同相的。

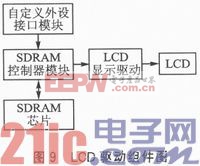

1.2.5 LCD顯示模塊

本設計采用的是一款3.5寸320×240的LQ035NC111 TFT液晶屏,此款LCD接口信號歸為5類:

①數(shù)字信號接口,如RESET、SPENA、SPCLK、SPDAT、Rx、Gx、Bx、HSYNC、VSYNC、DCLK和DE。此類接口主要是傳輸顯示數(shù)據(jù)給LCD面板。

②液晶的模式設置專用輸入接口,包括IF0、IF1、IF2等信號,它們的主要功能就是設置數(shù)據(jù)傳輸模式,本設計采用RGB數(shù)據(jù)傳輸。

③觸摸屏信號接口,是模擬信號,如Y1、X1、Y2、X2。

④電源接口。

⑤背光電源,即VBL+和VBL-。

圖9中各個模塊設計好后,打開SOPC,添加Nios II處理器、片內存儲器、系統(tǒng)ID和LCD顯示組件,分配好地址和中斷優(yōu)先級后,然后生成系統(tǒng)。把生成的系統(tǒng)和上面各模塊例化到頂層模塊中,分配好引腳,做好時序約束,編譯整個工程,完成硬件部分的設計。其中頂層模塊包括:

◆sys_ctrl模塊:系統(tǒng)復位信號和PLL控制模塊。

◆tcd1501d模塊:CCD系統(tǒng)模塊。

◆ad9844a模塊:A/D控制模塊。

◆sdram模塊:SDRAM封裝控制模塊。

◆sdfifo模塊:讀/寫SDRAM數(shù)據(jù)緩存FIFO模塊。

◆LCD模塊:LCD顯示模塊。

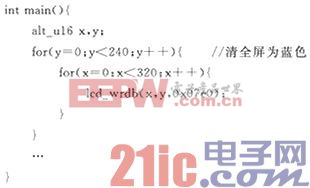

2 系統(tǒng)軟件程序

軟件程序主要是數(shù)據(jù)處理和LCD的顯示。數(shù)據(jù)過來后先清屏LCD,接下來就是坐標的一些定位與溢出處理,以滿足從左到右、從上到下的顯示順序。

(1)LGD寫數(shù)據(jù)函數(shù)

void lcd_wrdb(alt_u16 xaddr,alt_u16 yaddr,alt_u16 cor);

其中xaddr、yaddr、cor分別為X坐標地址、Y坐標地址和顯示的色彩。

(2)顯示函數(shù)

void print_db(alt_u16 row,alt_u16 col,alt_u8 *ptr,alt_u16 cor_b0,alt_u16 cor_q0);

該函數(shù)功能為在指定的位置顯示數(shù)據(jù)。

部分主函數(shù)程序如下:

結語

本文在Nios II處理器的基礎上實現(xiàn)了CCD采集系統(tǒng)的設計,經測試,該方法能較好地采集光電信號,并把圖像實時地顯示到LCD上,達到了本設計的預期目標。該方案穩(wěn)定可行,程序操作性強,在圖像采集和處理上具有一定的參考價值。

評論