高速數字光電耦合器HCPL-260L/060L及其應用

關鍵詞:HCPL-260L HCPL-060L 光電耦合器 LVTTL RS232

1 概述

現在,越來越多的產品向高速化、小型化、便攜式、低功耗方向發展,電源電壓僅有3.3V甚至更低的系統也正在蓬勃發展中,作為信號隔離的關系器件――光電耦合器,也必須使用相應的產品與之相適應。美國安捷倫科技有限公司(Agilent Technologies)生產的HCPL-262L/060L是與LVTTL/LVCMOS兼容的高速數字電耦合器,其速度可達15MBd。該器件的輸入端是GaAsP材料LED,輸出端是高增益信電極開路肖特基鉗位晶體管,該器件同時具有輸出使能控制。它的內部屏蔽結構可保證最小5kV/μs的共模瞬態抗擾度。HCPL-262L/060L可廣泛應用于高速數字邏輯接口、計算機外設接口、輸入/輸出緩存、A/D,D/A轉換數字隔離、線路接收器以及開關電源等方面。HCPL-260L/060L的主要特點如下:

*低功耗;

*速率高達15MBd;

*輸入電流可低至5mA;

*電源電壓范圍為2.7~3.3V;

*帶選通輸出功能;

*扇出系數為5個TTL負載;

*可在-40℃~85℃溫度范圍內無故障運行;

*已通過UL,CSA,VDE0884安全認證;

*HCPL-260L使用8腳DIP封裝;HCPL-060L使用SO-8封裝。

2 引腳功能及內部結構

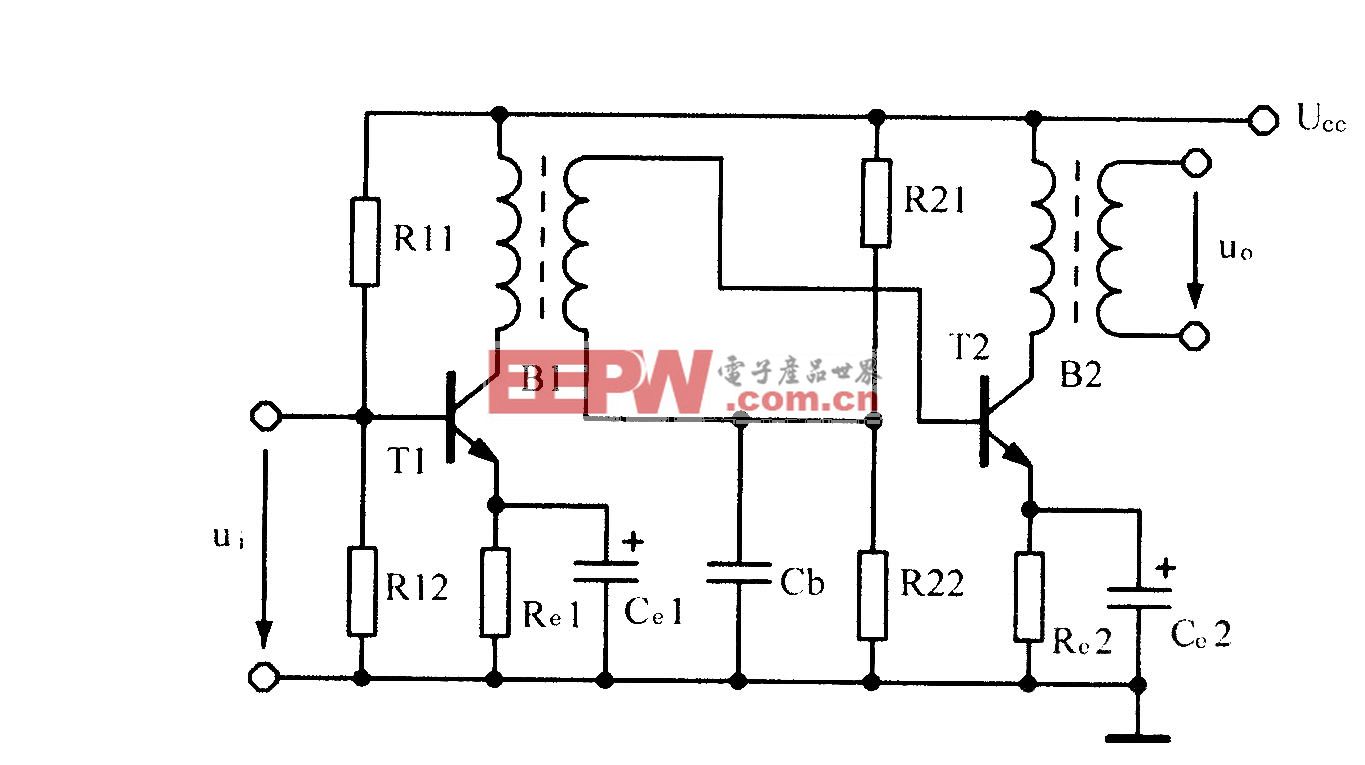

圖1是HCPL-260L/060L的引腳及內部結構圖,表1為其引腳功能說明,表2為正邏輯真值表。

表1 引腳名稱及功能說明

| 引腳號 | 引腳名稱 | 功 能 |

| 1 | NC | 空引腳 |

| 2 | ANODE | 輸入正 |

| 3 | CATHODE | 輸入負 |

| 4 | NC | 空引腳 |

| 5 | GND | 地 |

| 6 | VO(OUTPUT) | 輸出 |

| 7 | VE(ENABLE) | 輸出使能 |

| 8 | VCC | 電源 |

表2 真值表

| LED | ENABLE | OUTPUT |

| ON | H | L |

| L | H | |

| NC | L | |

| OFF | H | H |

| L | H | |

| NC | H |

3 應用設計

3.1 使用條件

為了保證器件可靠,使用時應按照表3所列條件進行設計。

表3 HCPL-260L/060L的使用條件

| 名 稱 | 符 號 | 最小值 | 最大值 | 單 位 |

| 使用溫度 | TA | -40 | 85 | ℃ |

| 輸入關態電流 | IFL | 0 | 250 | μA |

| 輸入開態電流 | IFH | 5 | 20 | mA |

| 電源電壓 | VCC | 2.7 | 3.3 | V |

| 低電平使能電壓 | VEL | 0 | 0.8 | V |

| 高電平使能電壓 | VEH | 2.0 | Vcc | V |

| 輸出端上拉電阻 | RL | 330 | 4k | Ω |

3.2 LVTTL接口電路

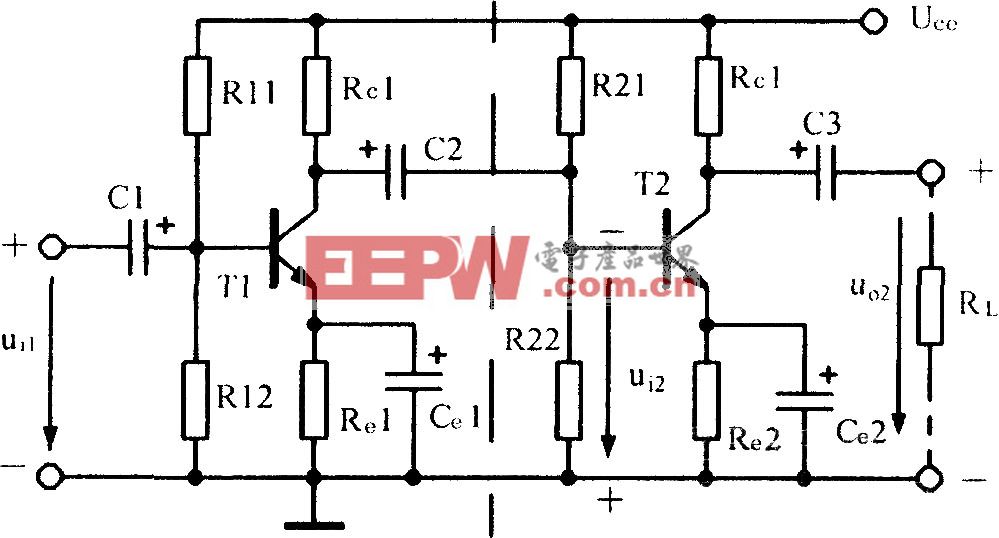

圖2是HCPL-260L/060L和LVTTL器件的典型接口電路。圖中,如果前級LVTTL器件是集電極開路輸出,則二極管1N4148可不用。

3.3 隔離的3.3V RS232接口電路

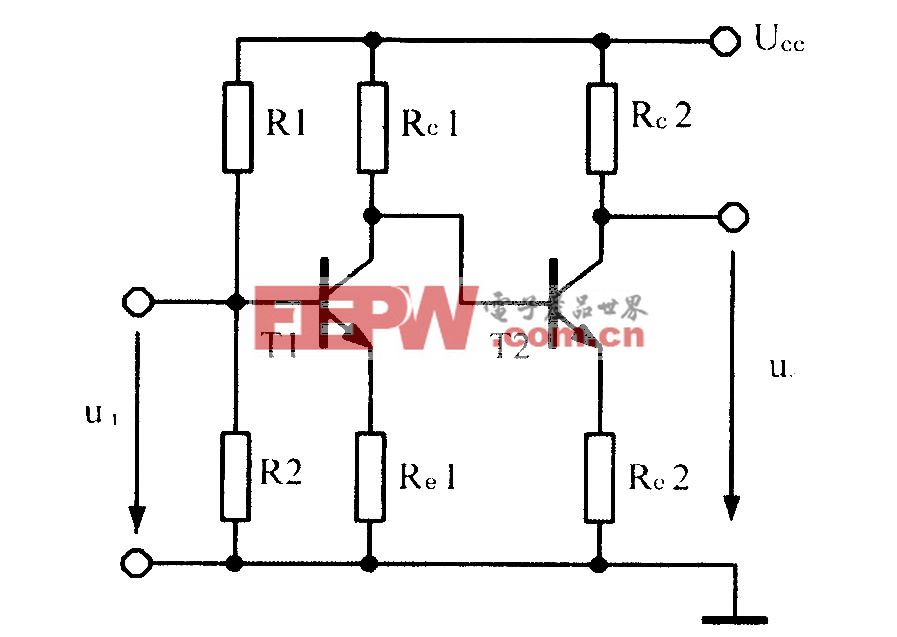

圖3所示的RS232接口電路的信號傳輸速度可達15MBd,為了保證該電路具有較好的共模抑制特性,HCPL-260L/060L的LED驅動電流至少應為5mA,并應將第7腳VE接至第8腳Vcc。另外,DS14C335應使用另一組電源供電。其中C1、C2為0.1μF,R1~R4的參數可由表3中的參數決定。

圖3 隔離的3.3V RS232接口電路

4 注意事項

首先,由于HCPL-260L/060L為靜電敏感器件,因此,拿取和焊接時應采取靜電防護措施。其次,在應用時,應在該器件第5腳和第8腳之間焊接一個0.1μF的瓷片電容,并且離光耦管腳應在10mm以內,以旁路電源噪聲。為了獲得較好的共模抑制特性,當不使用第7腳VE作輸出使能信號端地,不要將其懸空,而應接Vcc端。在此基礎上,如果想獲得更好的共模抑制特性,還應將第1腳和第4腳連接到輸入端的地。

上拉電阻相關文章:上拉電阻原理

評論