電信應用基于FPGA的功耗優化解決方案

Altera Quartus II 軟件功耗優化涉及到三個步驟。首先進行“功耗預知”綜合。功耗預知意味著軟件可以減少每個時鐘周期中要訪問的RAM模塊數量,還可以重新安排設計,以減少觸發頻率較高(或者易受干擾)的邏輯。

功耗預知綜合之后,Quartus II軟件對信號進行布線,減小電容,建立高功效DSP模塊配置,完成功耗預知布局布線。Quartus II軟件中的PowerPlay功耗優化功能指導適配器使用額外努力選項,利用專門的功耗體系結構特性,對設計進行功耗優化。使用時序約束,Quartus II軟件可保證設計中的關鍵通路在性能上達到最優,而時序不重要的通路在功耗上最優。

發揮FPGA的優勢

基于FPGA而不是代工線制造工藝進行芯片開發,可使專用芯片產品充分利用芯片制造的最新開發技術,來實現高功效解決方案。芯片供應商TPACK稱這一方法為SOFTSILICON,使用Stratix IV FPGA為電信系統供應商提供運營商級以太網數據包處理、流量管理和設計包映射芯片解決方案。

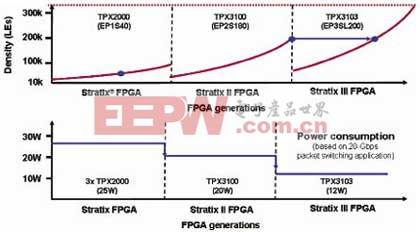

SOFTSILICON概念不但能夠開發容量更大的新芯片,而且還降低了現有設計的功耗。如圖1所示,TPACK的運營商級數據包引擎基于不同工藝尺寸的每一代Stratix系列FPGA,提供集成運營商級以太網數據包處理和流量管理功能。

圖1 降低現有芯片解決方案的功耗

從Stratix過渡到Stratix II FPGA,TPACK將運營商級數據包引擎容量從6Gbps (TPX2000)提高到20Gbps (TPX3100),降低了1Gbps交換容量的相對功耗。通過將這一解決方案從Stratix II導入到Stratix III FPGA (TPX3103)中,功耗降低了近40%。

SOFTSILICON方法的功耗優勢主要體現在以下兩個方面:采用最新的FPGA平臺,每Gbps以更低的相對功耗提供更大的交換容量;現有設計導入到最新的FPGA平臺,進一步降低功耗。這些優勢有助于滿足現在以及今后運營商對低功耗的嚴格要求。

發揮SOFTSILICON的優勢

FPGA的優勢使SOFTSILICON方案受益,不僅如此,FPGA還為標準無廠模式提供其他芯片開發方法,幫助專用芯片供應商滿足系統供應商和運營商的需求。

FPGA以前用于實現相對較少的功能(置入到ASSP中)或者作為“膠合邏輯”連接兩片不兼容的ASSP。但是在最近幾年,更多的復雜芯片方案嘗試采用FPGA,TPACK就是最早這樣做的公司之一。通過SOFTSILICON,TPACK提供了真正的ASSP 替代方案,具有更好的性能,特別是在功耗上。在這方面,集成也發揮了重要作用。在單芯片中集成更多的功能可以減小電路板面積,降低功耗,還可根據需要靈活更新解決方案,迅速修復故障。此外,需著重指出的是,ASSP集成的不足之處是出現故障的風險隨復雜度的升高而增大,而對于FPGA來說,則可迅速糾正這些故障,降低了集成的外在風險。

評論