智能型剩余電流保護器電磁兼容設計

具體從以下幾個方面進行設計:

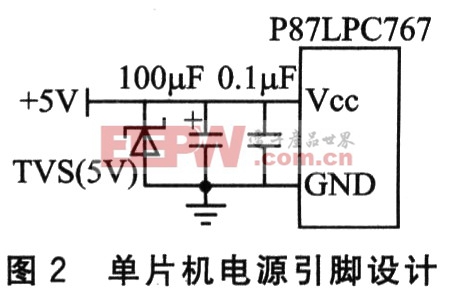

單片機工作電源和系統其他電路電源分開設計,避免其他電路對單片機工作電源產生影響,單片機工作電源設計留有足夠的余量,防止電源的波動影響單片機工作。在設計PCB板時,在單片機電源引腳接電容和瞬態電壓抑制器(TVS),如圖2所示。100 μF電解電容存儲的能量在電源波動時(降低)釋放出來,保持電源穩定;0.1μF的高頻電容可以吸收電源上的高頻干擾;TVS吸收瞬態浪涌功率,使兩極間的電壓箝位于一個預定值,保持單片機工作電源穩定。

復位電路采用P87LPC767單片機內部上電復位電路,避免干擾信號對復位電路的直接影響,只要單片機工作電源穩定,將不會出現誤復位引起的誤動作。中斷和其他I/O口電容進行濾波,減少干擾的影響。

系統軟件設計上,啟用P87LPC767內部的看門狗,防止PC受到干擾而失控,引起程序亂飛,進入“死循環”。在程序存儲空間的非程序區設置軟件陷阱,當由于干擾使操作系統失控而進入非程序區時,將引導指令轉向專門對程序出錯進行處理的程序,使程序納入正軌。

2 系統高頻干擾的消除――“采樣監測”法

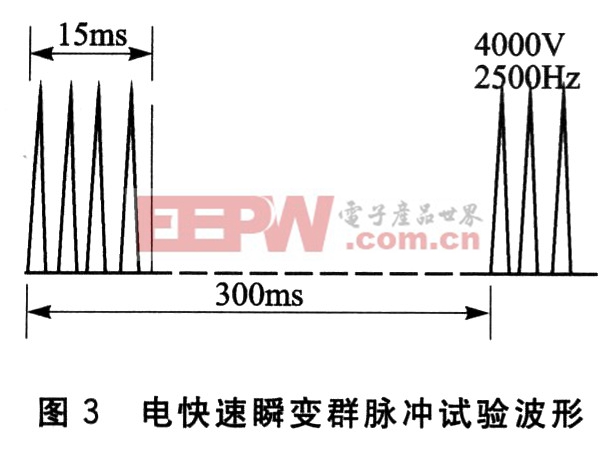

由于閃電、接地故障或切換電感性設備而引起的信號參數產生瞬時擾動,產生的高頻干擾信號主要是通過系統進線電源進入系統內部。檢測這方面的抗干擾能力,主要是通過“電快速瞬變脈沖群抗擾度試驗”驗證。根據低壓電器產品試驗標準要求,試驗時在供電輸入端疊加頻率為2 500 Hz,幅度4 000 V的群脈沖,分別進行相線、地線的差模、共模,正極性、負極性試驗,每項試驗時間均為1 min,群脈沖的波形如圖3所示。如果在“電快速瞬變脈沖群抗擾度試驗”過程中保護器不產生誤動作,則這方面的抗干擾能力就是合格的。

本系統利用“采樣監測”法對電源上的高頻干擾進行監測,給出相應的標志,由軟件程序進行相應的處理,避免保護器誤動作。詳細原理如下:

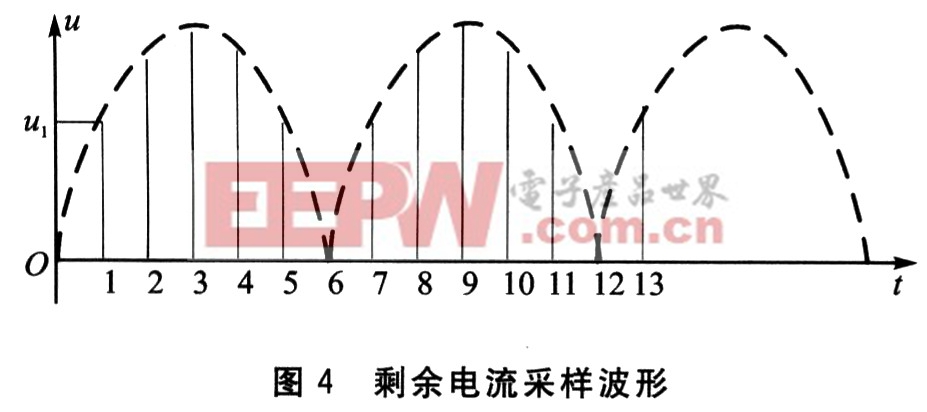

為保證剩余電流測量的實時性,該保護器采用數字采樣法測量剩余電流,將剩余電流信號轉換為圖4所示的波形,送給P87LPC767單片機內部的A/D進行采樣測量。

數字采樣方法具有數字濾波效果,對信號的通道干擾有抑制作用。設定每個周期采樣100個點,由定時器T0產生采樣時間間隔。將系統某相進線電源(如A相) 信號經過降壓、整形電路如圖5所示,轉換為方波信號。作為單片機中斷0的觸發信號,在正常情況下電源信號的頻率為50Hz左右,在兩次中斷期間,對剩余電流的采樣次數為100次。

基爾霍夫電流相關文章:基爾霍夫電流定律

電機保護器相關文章:電機保護器原理

評論