基于0.5 μm BCD工藝的欠壓鎖存電路設計

3 電路仿真與分析

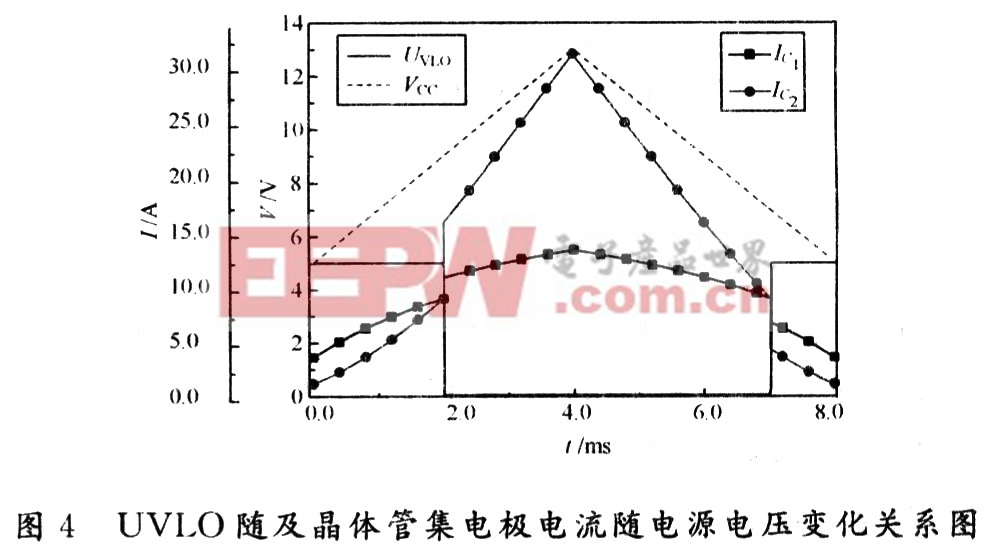

使用HSpice電路仿真軟件在CSMC 0.5μm BCD工藝庫下對UVLO電路進行仿真。由上面分析可知,UVLO電平翻轉與晶體管Q1,Q2集電極電流變化速度快慢密切相關,所以對帶隙基準晶體管上集電極電流變化做了如圖4的仿真。從圖4中可以明顯看出,在2 ms以前,IC1>IC2,UVLO輸出高電平。在2 ms時,兩個晶體管的電流都急劇變大,但是由于Q2管的跨導比Q1管小,所以很快,IC1IC2,UVLO輸出為低電平。下面可同理推出。

因為DC-DC芯片應用的溫度范圍比較大,而且工藝中的電阻、晶體管等受溫度影響也比較大,所以在實際設計中,應當充分考慮到這點。在此對UVLO不同溫度下進行仿真,盡可能把滯回區間的誤差縮小到很小的范圍內,以滿足DC-DC芯片在寬溫度范圍內工作。表1和圖5是對本文所設計的UVLO電路在-40℃,25℃,80℃和140℃下的仿真結果。從中可以看出,在25℃時,Von=9 V,Voff=7 V,滯回區間是2 V。在其他溫度下的偏差最大也不超過0.2 V,可見其最突出的優勢是可以在寬溫度范圍內工作而不失精度。

除此之外,當芯片發生欠壓鎖存時,芯片的功耗也是非常小的。這主要是因為當芯片發生欠壓鎖存時,芯片的其他部分都不工作,也就不消耗功率,UVLO電路的主要功耗是流過帶隙晶體管和R3,R4,R5,R6電阻的電流所產生,只要適當地調節這些電阻阻值就可以把功耗降低到最低,但是考慮到版圖的面積,實際仿真中的功耗可減小到150μW以下。

4 版圖設計

使用CSMC 0.5 μm BCD工藝技術,對UVLO電路設計版圖。由于利用帶隙基準原理,在要求精度較高的情況下,設計時應注意UVLO模塊與其他模塊隔離。與傳統的UVLO電路相比,最顯著的提升就是版圖面積大大縮小,只要工藝中包含高阻值的電阻類型,這種優勢就更為突出。

5 結 語

在此針對DC-DC電源管理系統所必須的欠壓所存功能,詳細介紹一種新的改進UVLO電路,相對于傳統的UVLO電路,它最突出的優點是不使用額外的帶隙基準源和復雜的數字邏輯,因此節省了芯片面積。HSpice仿真結果表明,它在-40~+140℃范圍內最大失真不超過2 %,因此可以在寬溫度范圍內工作。基本適用于各種類型的電源管理類芯片,對工藝要求也不高。

評論