基于0.5 μm BCD工藝的欠壓鎖存電路設計

一般的電源芯片上電啟動時,電源會通過輸入端的等效電阻和電容對其充電,使得電源芯片的電壓逐步上升,直到電壓上升到芯片的開啟電壓時電路正常工作。然而若系統(tǒng)的負載電流較大,有可能把電路的電壓拉低到開啟電壓以下,出現(xiàn)一開啟就關斷的情況。為了保證電路正常進入啟動狀態(tài)并且穩(wěn)定工作,同時也為了電路工作時電源電壓的波動不會對整個電路和系統(tǒng)造成損害,一般使用所謂的欠壓鎖存(Under Voltage LockOut,UVLO)電路對電源電壓實時監(jiān)控和鎖存。

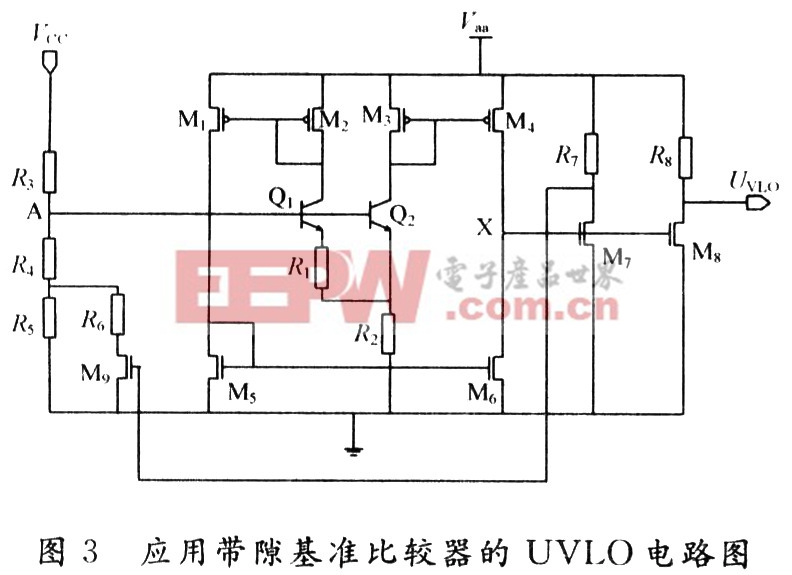

傳統(tǒng)電源管理類集成電路的欠壓鎖存電路的設計思路都是由比較器、帶隙基準參考電壓和一些邏輯部件構成的,其存在響應速度跟不上,功耗大,電路面積太大等問題。針對這些問題,設計一種新的欠壓鎖存電路,在不使用額外的基準電壓源和比較器以及復雜的數(shù)字邏輯的情況下,能夠達到UVLO的各項指標。它最主要的特點就是具有簡單的電路結構、高的反應速度、低的溫度敏感性和精準的門限電壓,同時版圖面積節(jié)省、功耗較低。

1 應用框圖與傳統(tǒng)電路結構

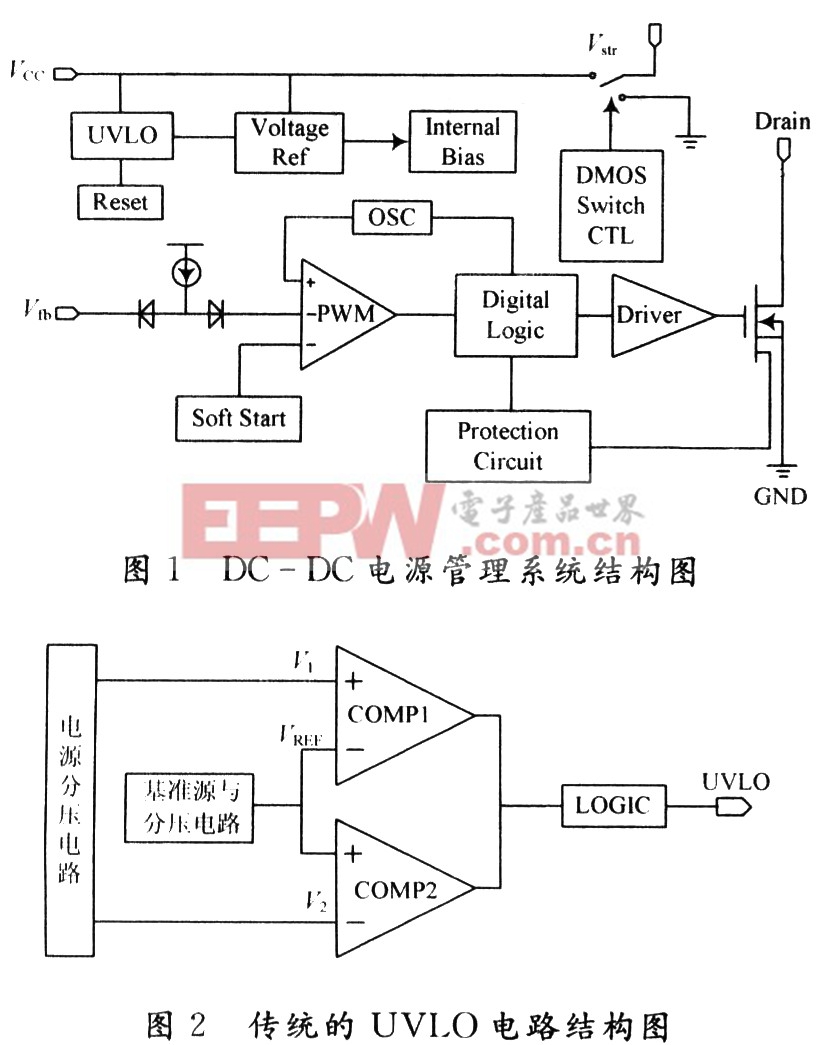

圖1是DC-DC電源管理系統(tǒng)結構圖。引腳Vstr直接與220 V交流整流器相連,最大耐壓650 V。只要芯片一上電,UVLO電路就實時地對電源電壓進行監(jiān)控。芯片剛上電時,電流通過引腳Vstr給引腳VCC外接電容充電,當充電到芯片預置的開啟電壓Von時,UVLO電路輸出電平發(fā)生翻轉,芯片內(nèi)部電路開始工作,Vstr對地短路,芯片電源由輔助變壓器對VCC外接電容充電供給。正如上所述,UVLO電路同時設置了一個關閉電壓Voff(VoffVon),用于防止由于系統(tǒng)負載電流較大而引起的一上電就關斷的情況。同時,由其他情況引起的電源電壓波動導致芯片電壓下降到Voff時,UVLO電平恢復,芯片不產(chǎn)生參考電源,所有邏輯操作都將被終止。

由此可見,UVLO電路實質上是一個遲滯電壓比較器,它必須具備反應速度靈敏,門限電壓穩(wěn)定,滯回區(qū)間合理,溫度漂移較低等特點。但是許多電源管理類集成電路的欠壓鎖存電路的設計思路都是由比較器、帶隙基準參考電壓和一些邏輯部件構成的,如圖2所示。不是響應速度跟不上,就是功耗太大,更重要的是這種電路使用帶隙基準參考電壓源和分壓電路,太過于復雜,使得電路面積太大而不利于降低成本。

在此提出一種基于0.5μm BCD工藝的UVLO電路,在不使用額外基準電壓源和比較器以及復雜數(shù)字邏輯的情況下,能夠達到UVLO的各項指標,其最主要的特點就是具有簡單的電路結構、高反應速度、低溫度敏感性和精準的門限電壓,同時版圖面積節(jié)省、功耗較低。

2 電路工作原理

如圖3為所設計的UVLO電路圖。

評論