高速ADC采集系統(tǒng)電路設(shè)計的考慮及分析

2 系統(tǒng)參數(shù)對系統(tǒng)設(shè)計的影響分析

首先,我們在設(shè)計高速ADC采樣系統(tǒng)電路時,重要的是要考慮到所有的參數(shù),要把每一個元件當(dāng)作前一級負載的一部份來考慮,并且當(dāng)源阻抗等于負載阻抗的共軛(見圖1)時,會產(chǎn)生最大的功率輸出。

下面重點分析系統(tǒng)參數(shù)對系統(tǒng)設(shè)計的影響:

(1)輸入阻抗:輸入阻抗是系統(tǒng)設(shè)計的特性阻抗,大多數(shù)情況下輸入阻抗為50 Ω,但可能會要求其它取值。變壓器是具有很好互阻性能的器件,其允許用戶根據(jù)需要耦合不同特性阻抗并且充分平衡系統(tǒng)的總負載。在放大器的設(shè)計電路里,阻抗被定義為輸入阻抗和輸出阻抗,放大器的阻抗特性不像變壓器那樣隨頻率變化。

(2)電壓駐波比(VSWR):電壓駐波比是一項無量綱參數(shù),用來表示在有用帶寬內(nèi)輸入功率反射到負載上的比率。當(dāng)負載ADC達到滿度輸入時,VSWR是一項用來確定所需要的輸入驅(qū)動能力的重要參數(shù)。

(3)通帶平坦度(或者增益均勻性):通帶平坦度指在規(guī)定帶寬內(nèi)增益響應(yīng)隨頻率的變化量(包括正波動和負波動),它可能會表現(xiàn)為波動,或者像Butterworth濾波器那樣簡單單調(diào)地下降,不管是哪一種情況,通常要求通帶平坦度小于或等于1 dB,這對于穩(wěn)定總系統(tǒng)增益至關(guān)重要。

(4)輸入驅(qū)動能力:輸入驅(qū)動能力是由特定應(yīng)用需要的系統(tǒng)增益決定。輸入驅(qū)動能力與帶寬指標密切相關(guān),并且依賴于所選擇的前端元件,例如濾波器、放大器或者變壓器,它們的特性是使輸入驅(qū)動能力最難達到要求水平的原因之一。

(5)信噪比(SNR):信噪比是在給定帶寬內(nèi),滿度信號的有效值與全部噪聲分量平方和的平方根的對數(shù)比,但是這不包括失真分量,從前端方面來看,SNR會隨著帶寬、時鐘抖動和增益的增加而降低,在高增益情況下,放大器在低增益時可能被忽略的噪聲分量會產(chǎn)生明顯作用。

(6)無雜散動態(tài)范圍(SFDR):無雜散動態(tài)范圍是滿度值的有效值與最大雜散頻譜分量的有效值之比。前端雜散有兩大危害,一個是造成放大器的非線性(或者使變壓器造成不理想平衡),它主要產(chǎn)生二次諧波失真;另一個是輸入失配,并且按照一定的增益放大這種失配(在高增益情況下,失配更加嚴重,并且放大寄生非線性作用),通常將這種情況看作三次諧波失真。

3 ADC固有電路的選擇對系統(tǒng)設(shè)計的影響分析

3.1 開關(guān)電容型ADC電路特性對系統(tǒng)設(shè)計的影響

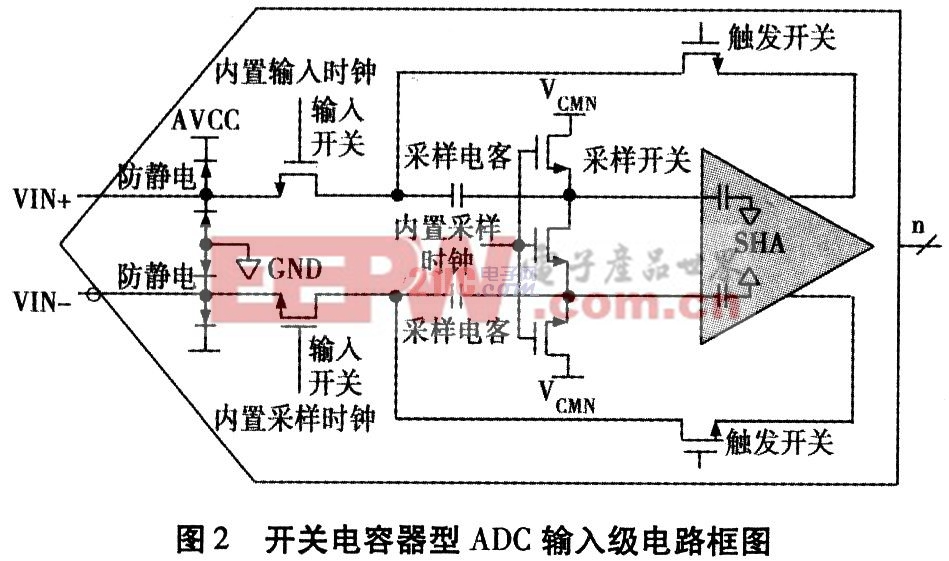

目前流行的CMOS開關(guān)電容ADC沒有內(nèi)置的輸入緩沖器,所以其功耗比帶緩沖器的ADC要低一些。外部信號源直接連接到ADC的內(nèi)置開關(guān)電容采樣保持(SHA)電路(見圖2)。這會產(chǎn)生兩個問題:第一,輸入阻抗隨時間變化,因為工作方式在采樣和保持之間不斷切換;第二,注入到采樣電容器的電荷會反射回信號源,這可能引起驅(qū)動電路里的無源濾波器的過渡延遲。

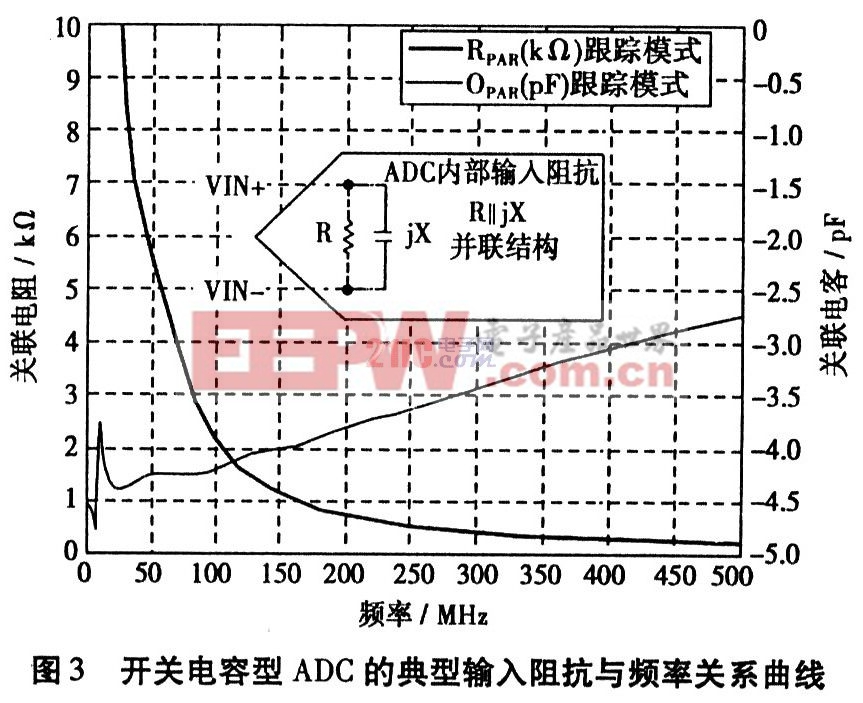

更為重要的是把外部網(wǎng)絡(luò)阻抗與ADC跟蹤模式阻抗匹配具有相當(dāng)?shù)碾y度,如圖3所示,輸入阻抗的實部或阻性阻抗(用藍色線表示)在低頻段(基帶)非常高(在幾千歐姆范圍內(nèi)),在超過100 MHz的頻段下降到2 kΩ以下。輸入阻抗的虛部或容性阻抗(用紅色線表示),一開始從一個相當(dāng)高的容性負載,然后在高頻段減小大約3 pF。要匹配這樣的輸入阻抗是一個相當(dāng)具有挑戰(zhàn)性的設(shè)計問題,尤其是在頻率高于100 MHz的情況下。

評論