低電壓帶隙基準電壓源技術解決方案

這樣,適當選擇R2/R1、R2/R3以及n的值,即可得到低電源電壓下的基準電平。

基于版圖的設計考慮,可選擇n為8,這樣可以更好地實現三極管的匹配,減小誤差。該電流源使用共源共刪結構,從而可以提高電流拷貝的精度以及減小電源電壓對Vref的影響,并在一定程度上有利于PSRR。

雖然CMOS工藝中的電阻絕對值會有偏差,但這里用到的是電阻的比值,所以要盡可能的做到比值的準確。具體方法是把R1、R2、R3都用單位電阻并聯串聯來表示。版圖設計時,應盡量把這些電阻放在一起,并在周圍加上dummy,以最大限度地減小工藝偏差對電阻比值的影響。

2.2 啟動電路

電路開啟前,可將Pup置為0,開關M1關斷,反相器輸入端為高電平,開關M2不開;當信號Pup置為1時,開關M1打開,反相器輸入端電壓被拉低,使開關M2開啟,P點電壓被拉低,帶隙基準電路部分開始工作,M3隨之開啟;此后由于M3開始工作,電阻Rstup上流過的電流把反相器輸入端電位抬高,超過反相器反向電壓時。輸出為低電位,開關M2關閉,啟動電路結束工作。M3與Rstup的選取是啟動電路值得注意的地方,M3鏡像而來的電流與Rstup的阻值乘積得到的電壓值必須在P點電壓穩定前足以使反相器輸出低電壓,并使開關M2關斷。

3 仿真分析

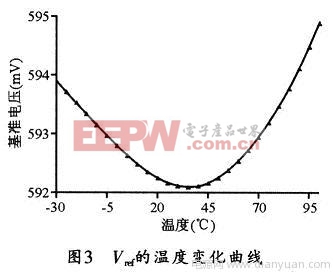

圖3為基準電壓幅度隨溫度變化的曲線,可以看到,從-30~100℃,Vref基本在3 mV以內波動,誤差范圍在5%以內。

圖4所示是本設計的PSRR仿真結果。從圖4可以看出,在低頻時,其PSRR約為-81 dB。

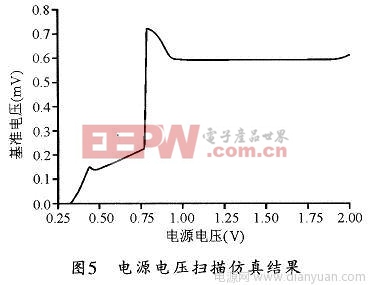

圖5是本設計的電源電壓掃描仿真結果。由圖可見,其電源電壓在1~1.8 V之間,基準電路都能很穩定的輸出約600 mV的電壓基準值。

4 結束語

本文給出了一個低電壓供電時的帶隙基準電壓源電路的設計方法。該電路通過對傳統帶隙基準電路的改進,使輸出基準電壓在600 mV仍然能滿足零溫度系數。本設計基于TSMC 0.13 μmC-MOS工藝。通過仿真,結果顯示:該電路在-30~100℃范圍內的溫度系數為12×10-6℃,低頻下的PSRR約為-81 dB。在供電為1~1.8 V范圍內,電路能夠工作正常,輸出電壓約600 mV。

評論