低電壓帶隙基準電壓源技術解決方案

本文采用一種低電壓帶隙基準結構。在TSMC0.13μm CMOS工藝條件下完成,包括核心電路、運算放大器、偏置及啟動電路的設計,并用Cadence Spectre對電路進行了仿真驗證。

本文引用地址:http://www.104case.com/article/180902.htm基準電壓是數模混合電路設計中一個不可缺少的參數,而帶隙基準電壓源又是產生這個電壓的最廣泛的解決方案。在大量手持設備應用的今天,低功耗的設計已成為現今電路設計的一大趨勢。隨著CMOS工藝尺寸的下降,數字電路的功耗和面積會顯著下降,但電源電壓的下降對模擬電路的設計提出新的挑戰。傳統的帶隙基準電壓源結構不再適應電源電壓的要求,所以,新的低電壓設計方案應運而生。

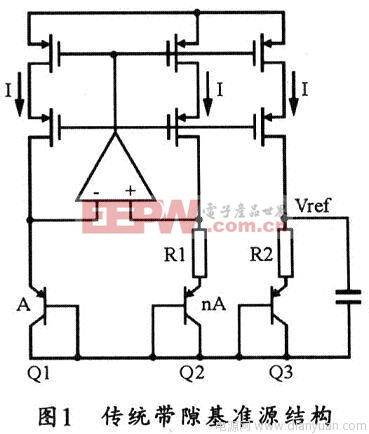

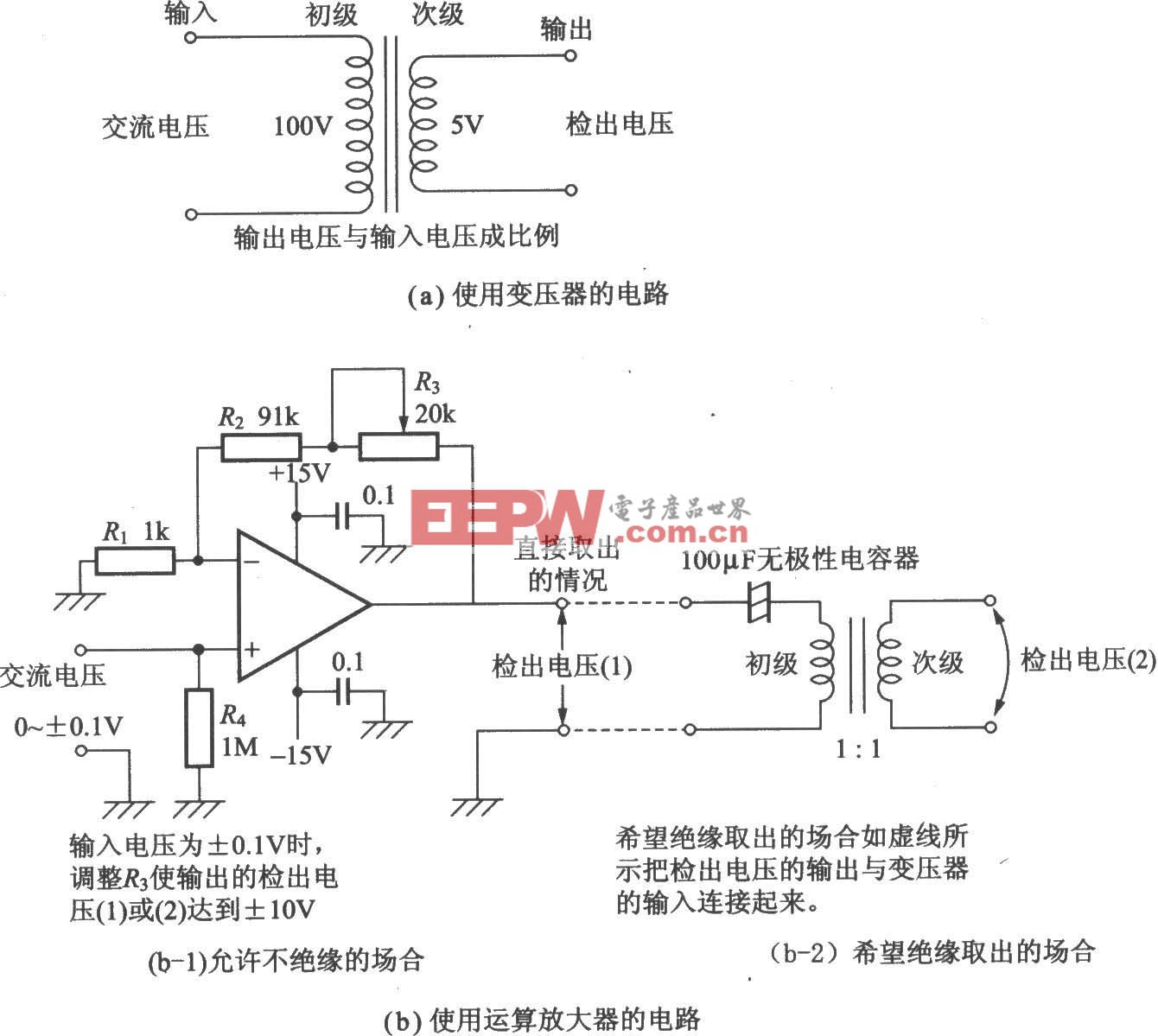

1 傳統帶隙基準電壓源的工作原理

傳統帶隙基準電壓源的工作原理是利用兩個溫度系數相抵消來產生一個零溫度系數的直流電壓。圖1所示是傳統的帶隙基準電壓源的核心部分的結構。其中雙極型晶體管Q2的面積是Q1的n倍。

假設運算放大器的增益足夠高,在忽略電路失調的情況下,其輸入端的電平近似相等,則有:

VBE1=VBE2+IR1 (1)

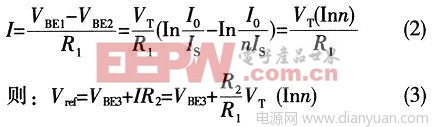

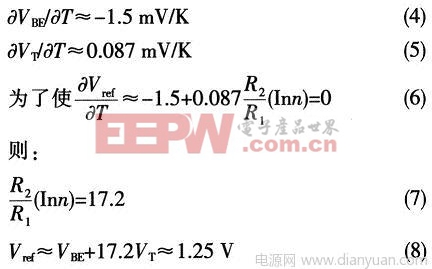

其中,VBE具有負溫度系數,VT具有正溫度系數,這樣,通過調節n和R2/R1,就可以使Vref得到一個零溫度系數的值。一般在室溫下,有:

但在0.13μm的CMOS工藝下,低電壓MOS管的供電電壓在1.2 V左右,因此,傳統的帶隙基準電壓源結構已不再適用。

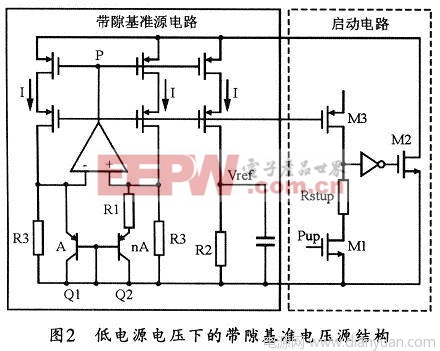

2 低電源帶隙基準電壓源的工作原理

低電源電壓下的帶隙基準電壓源的核心思想與傳統結構的帶隙基準相同,也是借助工藝參數隨溫度變化的特性來產生正負兩種溫度系數的電壓,從而達到零溫度系數的目的。圖2所示是低電壓下帶隙基準電壓源的核心部分電路,包括基準電壓產生部分和啟動電路部分。

2.1 帶隙基準源電路

由于放大器的輸入端電平近似相等,故由電流鏡像原理可得到如下等式:

評論