基于FPGA的工控領域監控系統設計

AD7705包括6個用戶可通過串口訪問的片內寄存器。其中第一個是通訊寄存器,用于管理通道選擇,決定下一個操作是讀操作還是寫操作,以及下一次讀或寫哪一個寄存器。所有與器件的通訊必須從寫通訊寄存器開始。上電或復位后,器件將等待在通訊寄存器上進行一次寫操作;

第二個是設置寄存器,用于決定校準模式、增益設置、單/雙極性輸入以及緩沖模式;

第三個是時鐘寄存器,其中包括濾波器選擇位和時鐘控制位;

第四個是數據寄存器,器件輸出的數據從這個寄存器讀出;

第五個是零標度校準寄存器,AD7705包含兩組獨立的零標度寄存器,每個零標度寄存器負責一個輸入通道。它們都是24位讀,寫寄存器;

第六個是滿標度校準寄存器,AD7705包含兩組獨立的滿標度寄存器,每個滿標度寄存器負責一個輸入通道。它們都是24位讀/寫寄存器。本文引用地址:http://www.104case.com/article/180882.htm

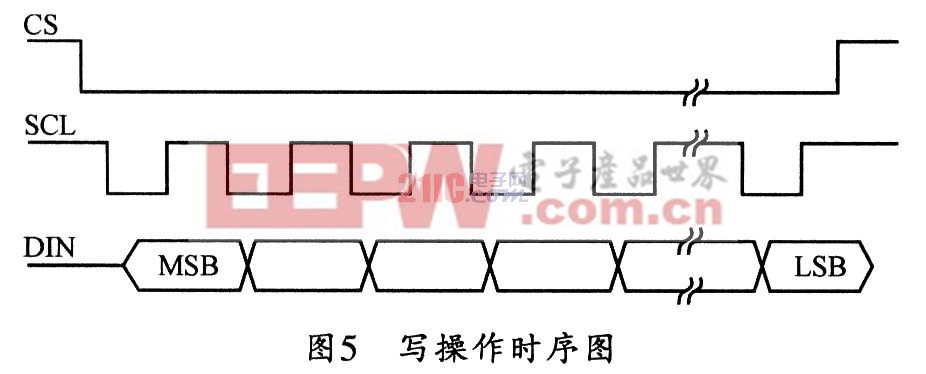

AD7705的寫操作時序圖如圖5所示。在將片選端CS拉低后,即可在串行時鐘的上升沿發送數據,發送數據時,高位在前。

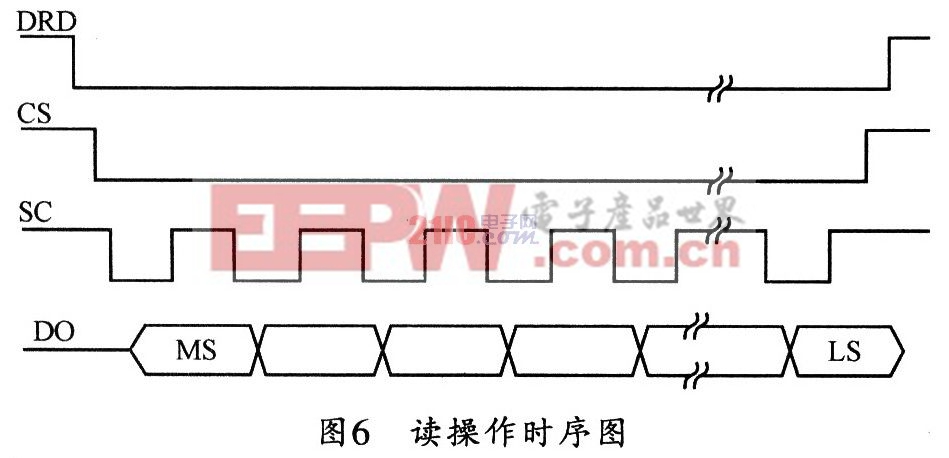

AD7705的讀操作時序圖如圖6所示。當在AD7705的DRDY信號腳檢測到邏輯低電平時,表示可以從AD7705的數據寄存器獲取新的輸出字,當完成對一個完全的輸出字的讀操作后,DRDY引腳立即回到高電平。如果在兩次輸出更新之間,不發生數據輸出,DRDY將在下一次輸出更新前500個輸入時鐘時間返回高電平。DRDY處于高電平時,不能進行讀操作。當數據更新后,DRDY又返回低電平。

2.2 FPGA接口的軟件設計

FPGA與AD7705共有5個接口引腳,分別為片選端CS、串行時鐘端SCLK、串行數據輸入端DIN、串行數據輸出端DOUT和串行數據請求端

DRDY。

讀AD7705的數據寄存器前,需先設置其時鐘寄存器和設置寄存器,下面以1通道為例來簡要說明,首先向AD7705發送串行數據0x20,表示下一操作選擇時鐘寄存器,接著發送串行數據0x0C,設置時鐘為2分頻,然后發送Oxl0,表示下一操作選擇設置寄存器,接著發送串行數據0x44,表示設置寄存器模式為自校準,增益l,單極性,無緩沖,然后再向AD7705發送0x38,表示可以讀通道1的數據寄存器,并等待AD7705的DRDY變低,然后發送16個時鐘,以讀取通道1的16位轉換數據。通道2的數據讀取與通道1的數據讀取相似,發送的數據分別為0x21,0x0C,

0x11,0x44,0x39。

3 結束語

本文用有限狀態機在FPGA上實現了對有SPI接口的AD轉換器AD7705的接口應用,并對AD7705的兩路輸入信號進行了實時采集。事實上,選用通用I/O口模擬SPI時序,相比標準SPI接口IP核更為簡潔,可以節約FPGA的片上資源。由于AD7705提供有雙通道、低成本、高分辨率的模數轉換功能,因此,采用∑-△結構實現模數轉換,可使得該器件在噪音環境下免受干擾,因而很適合于工業控制應用。

評論