基于FPGA的可編程PWM電路設計

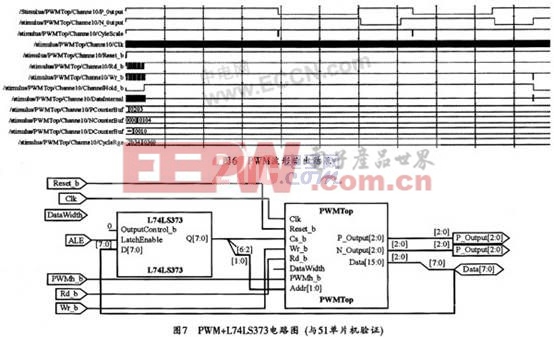

4.1 PWM的仿真

ModeslSim仿真主要觀察PWM電路的雙向IO端口以及PWM的Regs讀寫控制時序。對于雙向端口的數據交換,可以采用讀寫控制結合三態門來完好地解決。而對于大量的Regs讀寫操作,則應通過模擬單片機對外圍器件進行操作,并利用Task調用的方式來實現。本文的讀寫操作仿真結果如圖5所示。

從圖5可以看到,當采用16 bits讀寫時,各寄存器通過內部DataInternal數據總線的傳輸過程與電路設計要求完全一致。RWLogic與DataInterface模塊的功能完全符合設計預想。

從圖6所示的PWM波形仿真結果可見,PWM輸出信號在ClkGen的CycleScale信號控制下,其周期輸出編程設定的PWM波形與之完全一致,同時還能異步響應ChannelHold_b信號的輸出控制。

4.2 PWM的驗證

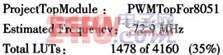

PWM的FPGA驗證可采用8 bits數據接口,并用89C51做外圍控制器(12 MHz)來對PWM進行操作。為了方便與單片機的接口,可將74LS373鎖存器內置到PWM中,其整個數字部分設計如圖7所示。

5 結束語

通過Synplify Pro編譯后,其最后的結果為:

該方案的整個電路設計占用FPGA資源的35%。對于51系列的單片機而言,該PWM電路可運行的頻率遠遠超過系統頻率。因此,在讀寫時序上完全可以保證整個設計的可靠性。

如果將編譯后的pof文件下載到APEX20KEEP20K100E TQ144-2X(Altera)fpga驗證板,并采用40 MHz的FPGA時鐘,那么,根據軟件仿真的步驟,再將讀寫操作轉換為單片機程序燒錄到單片機,就可通過示波器清楚的看到,其實際輸出與設計完全一致,非常好地實現了當初的設計要求。

pwm相關文章:pwm原理

評論