與萬用表結合使用的FET VP、VOO檢驗器

電路的功能

本文引用地址:http://www.104case.com/article/180791.htm

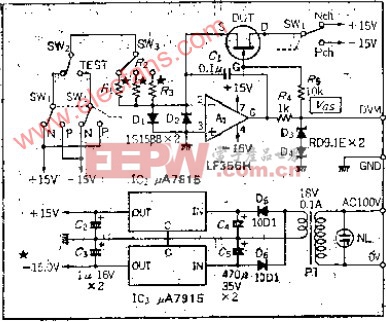

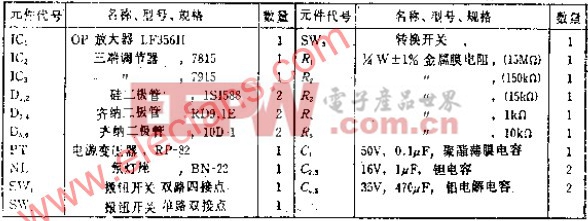

場效晶體管漏極飽和電流IDSS和夾斷電壓VP等有很大差別,所以確定置偏很麻煩。雖然在生產廠已分了幾種等級,但一個等級內仍有差別,如果在組裝電路之前測量實際工作電流狀態(tài)下的VP和VOS則比較方便。測量時,用轉換開關選擇電阻R1~3,設定工作電流,R值可用R=15/ID計算。

電路工作原理

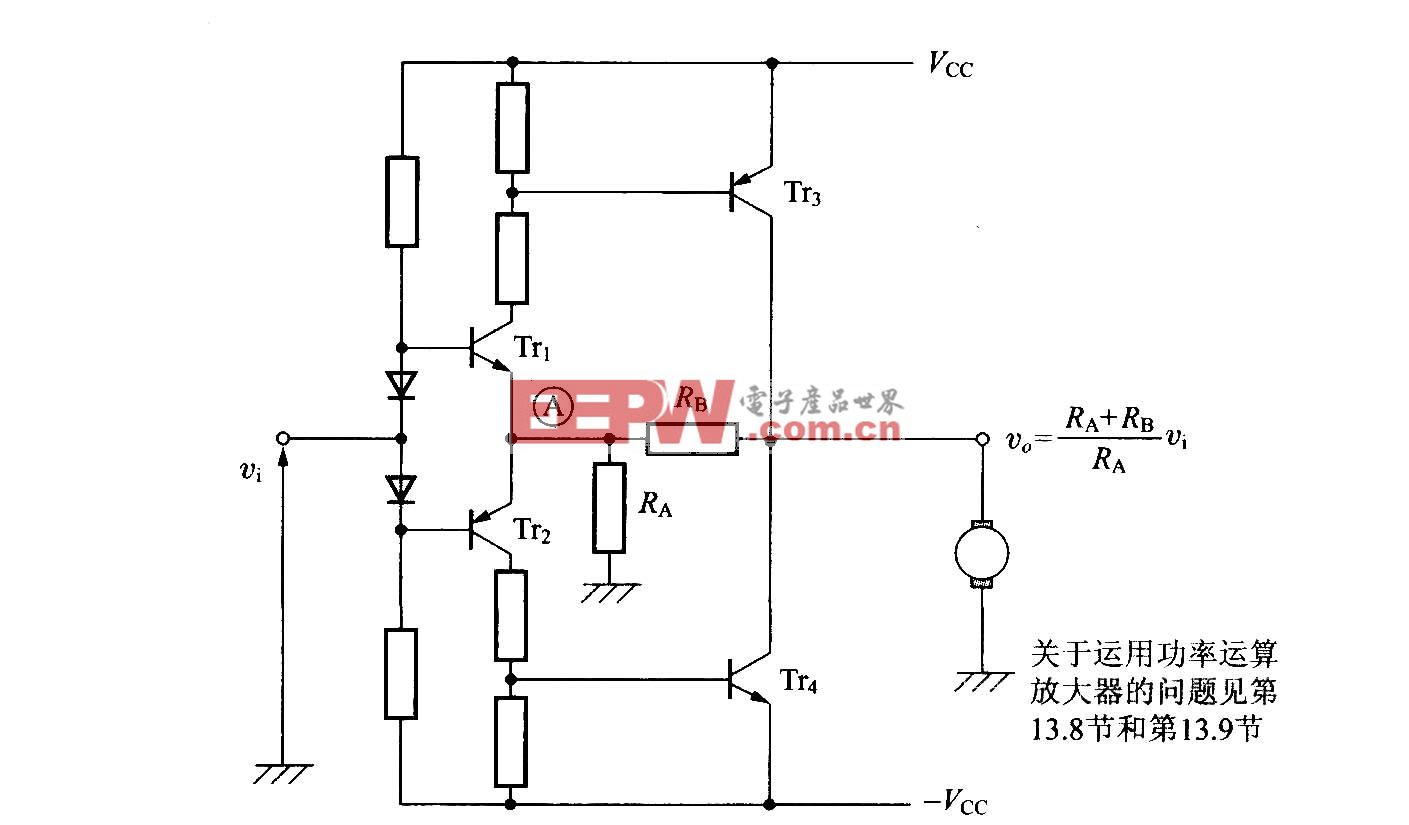

在OP放大器反相放大電路中,使流過反饋回路的電流與輸入電阻確定的電流相等,因此FET漏極電流EB由柵極電壓VGS確定。即OP放大器A1構成伺服電路,用A1的輸出控制反相輸入端的電位,使基等于零。

齊納二極管D3和D4產生±9V的電壓對被測對象(DUT)的柵極電壓進行拖箝位使電路不至加異常電壓。R5是限流電阻,用來控制柵極電流,使基不至過大(通常幾乎無電流流過)。

FET有N溝道和P溝道兩種型式,因此可用SW1切換輸入電壓的極性,滿足這兩種型號的需要。測試開關SW2在無DUT時,柵極端子電壓高于夾斷電壓,OP放大器的輸出對于NOA來說為負,對于POH為正,在進行正常測試時,OP放大器輸出為VGS。工作電流ID為1UA時,R1=15/10的-6次方=15M,IB=100UA時,R2=15/10的-4=150K,ID為1MA時,R3=15/10的3次方=15K,應根據(jù)使用要求計算R1~R3。

注釋

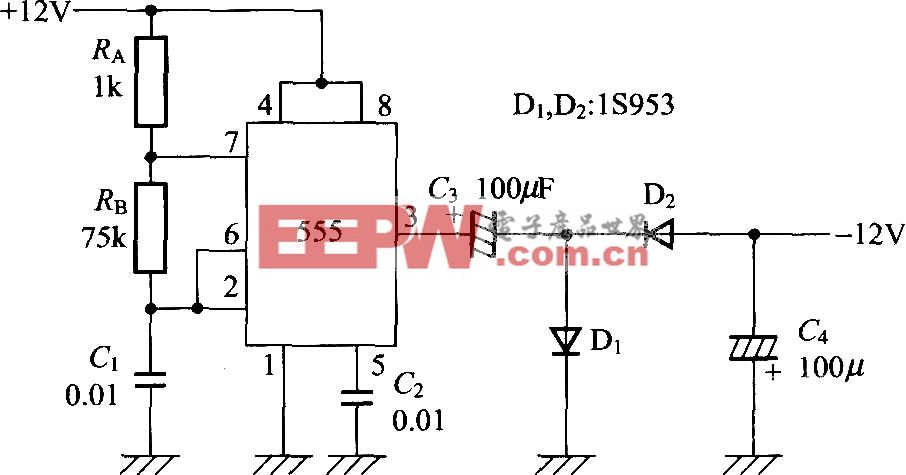

FET的自編電路

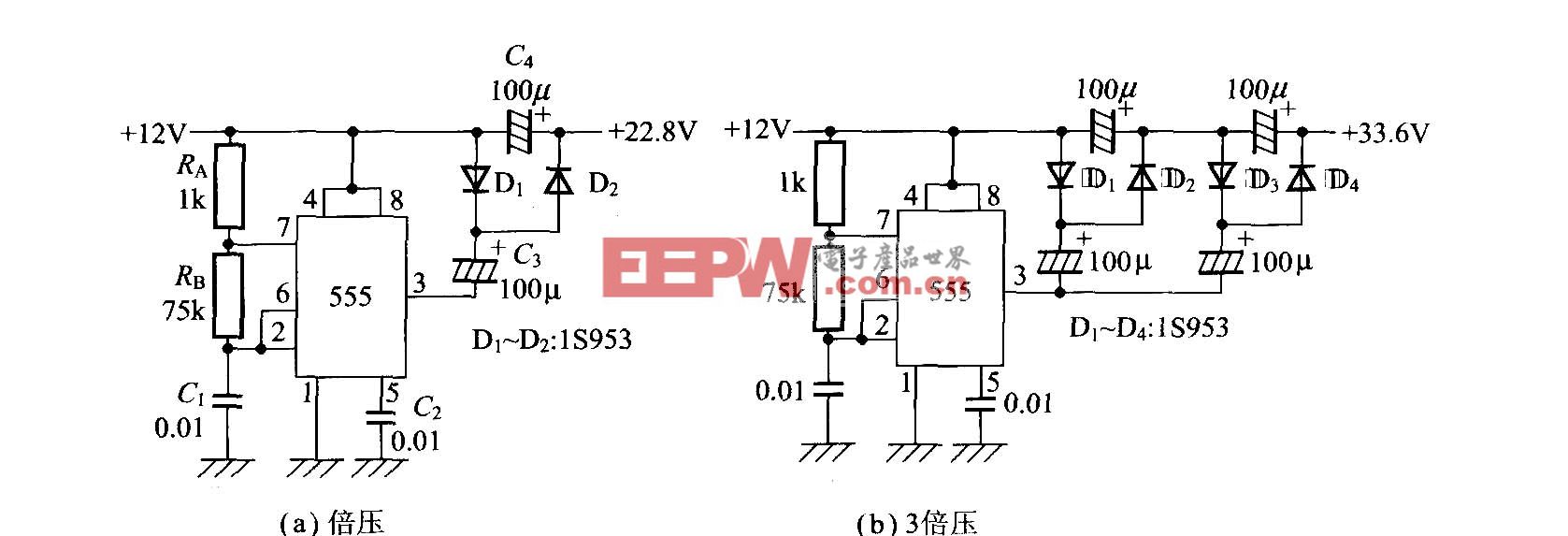

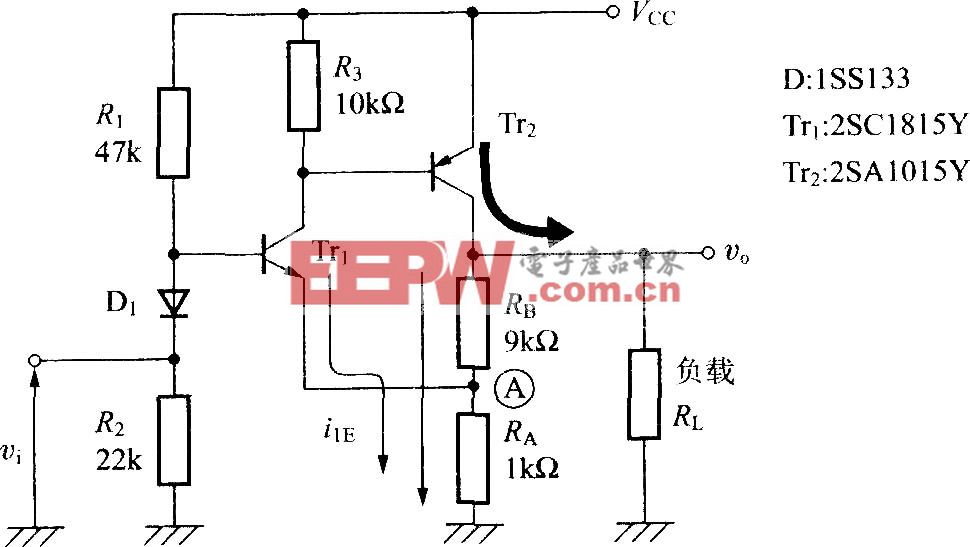

圖中所示為普通N溝通J-FET自偏電路,由于夾斷電壓VP或漏極飽和電流IDSS的誤差,使置偏點Q發(fā)生變化。

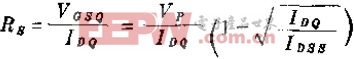

若把源極電阻RS兩端產生的電壓作為柵極置偏,設定Q點,考慮VP和IDSS的影響后,可用下式大約計算出RS

RS越大,越能吸收誤差,但由于受工作電流IDQ的限制,須選用適當?shù)淖柚祷蚋挠霉潭ㄖ闷娐贰?/font>

評論