一種用于高速高精度ADC的電壓基準(zhǔn)源設(shè)計(jì)

帶隙基準(zhǔn)電路的電源電壓抑制比可以表示為:PSRR=O(1-Add)/AVO,其中AV為運(yùn)放的開環(huán)增益,Add為運(yùn)放的輸出與電源電Ndd之比。因此,為了提高PSRR,可以采取三種措施:一是增加運(yùn)放的開環(huán)增益Av;二是改進(jìn)電路結(jié)構(gòu)使運(yùn)放的Add趨近1;三是引入預(yù)校正技術(shù),即通過(guò)一個(gè)反饋電路將電源電壓穩(wěn)定在Vreg,并由Vreg為基準(zhǔn)電路供電,以有效提高PSRR。

本文的電路結(jié)構(gòu)除采用共源共柵電流鏡技術(shù)外,所加入的電源抑制比提高電路還可使運(yùn)放的Add趨近1,從而大大提高基準(zhǔn)源的電源抑制比。

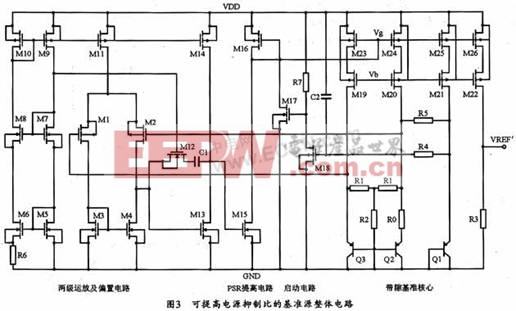

電源抑制比提高電路的具體結(jié)構(gòu)如圖3所示,它主要由M15,M16構(gòu)成。作為M16負(fù)載的M為二極管接法,具有低輸出阻抗,可在提高環(huán)路增益的同時(shí),把電源紋波引入到環(huán)路中。由于以PMOS作為輸入管的兩級(jí)密勒補(bǔ)償運(yùn)放的PSR約為0,因此,Vg的PSR主要由PSR提高電路決定,具體表示為:

從上式可知,VG跟隨Vdd變化,使M23,M24的柵源電壓保持恒定,從而提高基準(zhǔn)電壓的PSR。

3 電路仿真

3.1 溫度系數(shù)的仿真

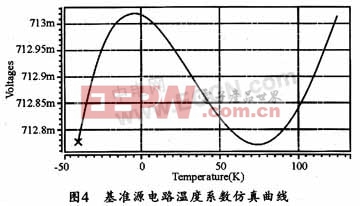

通過(guò)Hspice仿真軟件可對(duì)上述基準(zhǔn)源的整體電路進(jìn)行溫度系數(shù)仿真,圖4所示是其溫度系數(shù)仿真曲線,由圖可以看出,二階曲率補(bǔ)償技術(shù)可有效降低基準(zhǔn)源的溫度,在-40℃~125℃的溫度范圍內(nèi),其電壓基準(zhǔn)輸出變化為0.26 mV,溫度系數(shù)為2.13 ppm/℃,完全可滿足12位100 MspsADC的系統(tǒng)要求。

3.2 PSRR的仿真

對(duì)比加入電源抑制比提高電路前后的電壓基準(zhǔn)源電路的電源抑制比仿真結(jié)果可以發(fā)現(xiàn):沒有加入PSR提高電路的電壓基準(zhǔn)源的電源抑制比在低頻條件下可達(dá)到-72 dB,在100 kHz條件下為-62 dB;加入PSR提高電路后,電壓基準(zhǔn)源的電源抑制比達(dá)到-101dB,在100 kHz的條件下,仍然能夠達(dá)到-81 dB。可以看出,引入PSR提高電路后,其PSR提高了29 dB。

4 結(jié)束語(yǔ)

本文對(duì)電壓基準(zhǔn)源引起的ADC系統(tǒng)的DNL誤差進(jìn)行了建模分析,提出了一種采用二階曲率補(bǔ)償技術(shù)的電壓基準(zhǔn)源電路,該電路運(yùn)用低噪聲兩級(jí)運(yùn)放進(jìn)行箝位,同時(shí)在采用共源共柵電流鏡技術(shù)的基礎(chǔ)上加入了PSR提高電路。通過(guò)在基于TSMC 1.8 V 0.18 μm標(biāo)準(zhǔn)CMOS工藝條件下的仿真結(jié)果表明,該電路的溫度系數(shù)為2.13 ppm/℃,電源抑制比在低頻條件下可達(dá)到-101 dB,可以滿足12位100 Msps ADC的系統(tǒng)要求。

評(píng)論