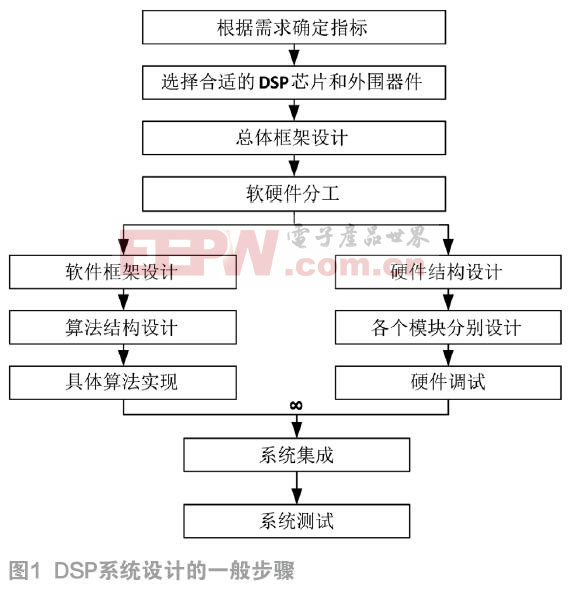

基于SOPC的SPWM脈沖發生器的實現

圖3為SPWM脈沖發生器中SPWM模塊的原理圖。本文引用地址:http://www.104case.com/article/180716.htm

本系統采用載波信號和調制信號不保持同步的異步調制方式。在異步調制方式中,通常保持載波頻率固定不變,即三角載波的頻率保持不變。三角載波的數字化是利用計數器來產生階梯狀的數字化三角載波,其核心部件是一個無符號加減計數器。利用其循環加減計數來產生階梯狀的數字化三角載波。計數器先執行加法,從0計數到某一值。在本系統中設定為255,再執行減法計數從255到0,從而實現三角載波。本系統中三角載波的峰峰值為255。設O為數字化三角載波的峰值,TCLK為加減計數器的時鐘周期,Ts為三角載波周期,則這3者之間的關系為:

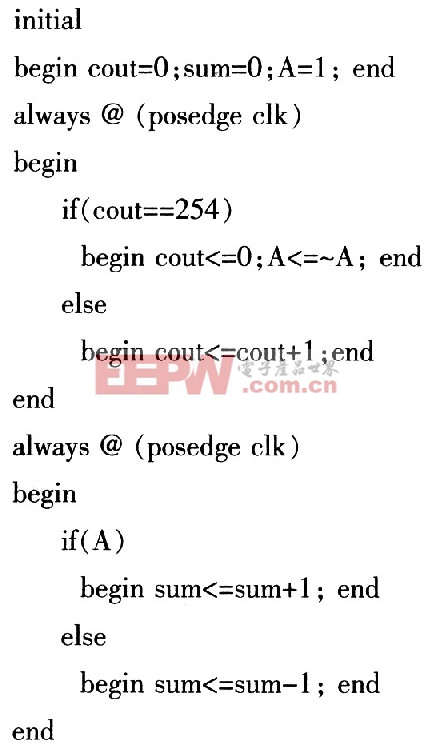

下面給出Verilog HDL設計的三角載波發生器的部分程序。

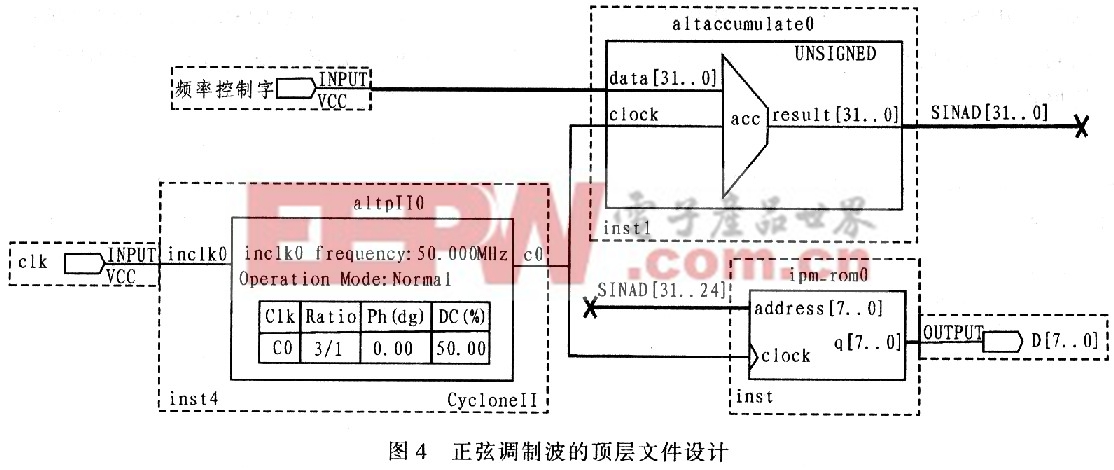

正弦調制波產生采用直接數字頻率合成器DDS方案實現。DDS技術是一種采用數字化技術、通過控制相位的變化速度,直接產生各種不同頻率和不同幅度信號的頻率合成方法。DDS具有較高的頻率分辨率,可實現快速的頻率切換且在頻率改變時能夠保持相位的連續,很容易實現頻率、相位和幅度的數控調制。DDS系統的核心是相位累加器,它由一個加法器和一個相位寄存器組成,每來一個時鐘,相位寄存器以步長增加,相位寄存器的輸出與相位控制字相加,然后輸入到正弦查找表地址上,正弦查找表包含一個周期正弦波的數字幅度信息,每個地址對應正弦波中0°~360°范圍的一個相應點。在FPGA內部開辟一塊ROM區域,將通過程序生成的離散時間正弦波幅值存入其中。圖4所示為正弦調制波的頂層文件設計。

在本系統中,將256個離散時間正弦波幅值存入ROM中。在系統上電后,根據設定的頻率按照相位與地址一一對應的關系從表中依次讀出預先存好的幅值。本系統采用異步調制方式,三角載波的幅值與頻率是固定的,這樣通過改變正弦調制波的頻率與幅值,則改變系統的載波比與調制。

幅度調節模塊是控制正弦波的輸出幅度,從而控制SPWM的脈沖寬度。這一功能是通過并行乘法器實現的。它實現容易,運算速度快,可靠性高,可以滿足系統的高效要求。在系統中乘法器對正弦函數表中取出的正弦幅值進行調制深度加權調整。設某時刻正弦調制波幅值為YIN相應的調制度所對應的一整數為λ,則此時輸出正弦信號的幅值YOUT:

式中,λ的取值范圍為0~255。因為正弦離散時間幅值范圍為0~255,所以通過一個8位的并行乘法器實現λYIN。在數字電路中將數據右移1位等同于數值除以2的效果,所以取λYIN結果的高8位作為YOUT的值,以此實現除以256的效果。

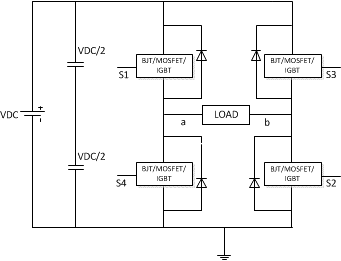

數字比較器就是將三角載波信號的幅值與正弦調制信號的幅值進行比較。在系統中,三角載波信號與正弦調制信號均是以數字方式實現的,所以將三角載波的計數值與正弦調制信號的幅值進行比較,然后根據二者數值的大小比較得出“1”與“0”兩種邏輯量。在正弦調制信號與三角載波信號兩個相鄰的交點之間,若正弦波幅值數據大于三角波幅值數據,則通過比較后,所得的邏輯量為“1”,反之則為“0”。

評論