基于可編程計數器的時序邏輯電路設計

各種MSI中規模數字集成電路都有自己的主要特性和應用目標,如果進行非常規使用,則改變它的使用方向,就可進一步發揮其功能和作用。擴展專用集成電路的應用領域是一項有實際意義的研究。本文研究了MSI可編程計數器改變應用方向的邏輯修改方法及時序邏輯電路的設計技術。

1 基本原理

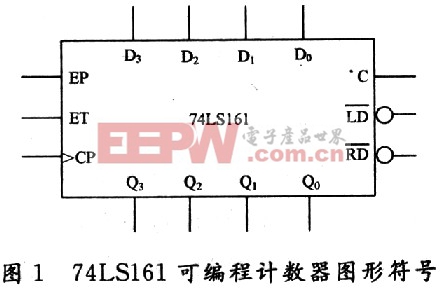

74LSl61是可編程中規模同步4位二進制加法計數器,圖1為其圖形符號。其中,Q3,Q2,Q1,Q0為計數狀態輸出端;C為進位輸出端;EP,ET為計數控制端;

表1為可編程計數器74LSl61的功能表。

由表1可知,在![]() 條件下,74LSl61可編程計數器由EP,ET及

條件下,74LSl61可編程計數器由EP,ET及![]() 控制具有計數、預置數和保持三種功能。

控制具有計數、預置數和保持三種功能。

用74LSl61可編程計數器Q3Q2Q1Q0端的代碼組合表示時序邏輯電路的各個狀態,由輸入變量控制EP,ET及![]() 端,綜合利用計數、置數、保持功能,使計數器的狀態變化滿足所要求的時序,即用計數功能實現“次態=現態+l”的二進制時序關系,用預置數功能實現“次態=預置數”的非二進制時序關系,用保持功能實現“次態=現態”的自循環時序關系,可實現一般時序邏輯電路。

端,綜合利用計數、置數、保持功能,使計數器的狀態變化滿足所要求的時序,即用計數功能實現“次態=現態+l”的二進制時序關系,用預置數功能實現“次態=預置數”的非二進制時序關系,用保持功能實現“次態=現態”的自循環時序關系,可實現一般時序邏輯電路。

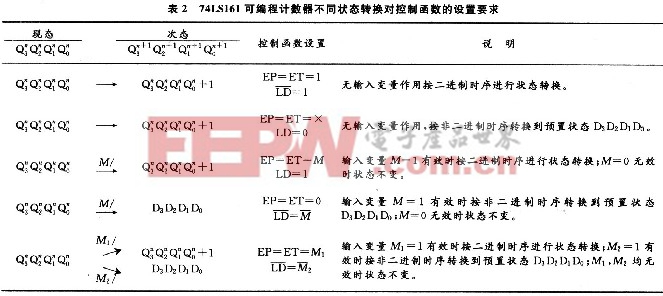

1.1 可編程計數器狀態轉換對控制函數的要求

由表1所示的功能表,可確定74LSl61可編程計數器各種狀態轉換時對控制函數的要求,如表2所示。

1.2 基于可編程計數器時序邏輯電路的基本形式

用1個74LSl61可編程計數器和2個16選1數據選擇器可構成多輸入時序邏輯電路的基本形式,如圖2所示。

評論