低功耗10位100 MHz流水線A/D轉換器設計

3 性能結果與分析

本文利用運放共享技術設計了一個10位100 MHz的流水線ADC,該ADC的最前端是一個輸入帶寬很大的采樣保持電路,之后的8級MDAC輸出利用運放共享技術使用了4個運算放大器,產生16位數字輸出。最后一級為一個2位的FLASH模/數轉換器。最終產生的18位輸出經延遲對準后輸入數字修正電路得到最后的10位數字編碼。

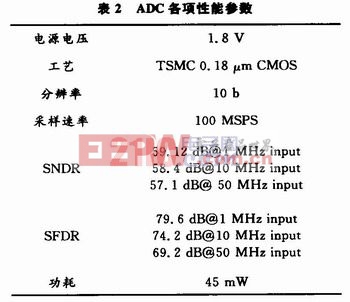

本設計采用的是TSMC 0.18μm,混合信號1P6MCMOS工藝模型,提供MIM(metal-insulator-metal)結構電容,采用電源電壓為1.8 V。使用Spectre進行驗證。結果可得在100 MHz采樣頻率下,采用電容縮放技術后整個ADC電路的功耗為45 mW。

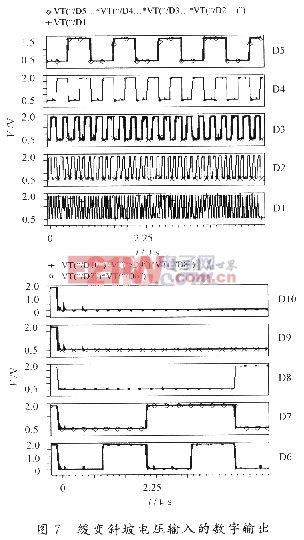

首先輸入一個緩變斜坡電壓進入模/數轉換器,斜坡的變化時間和電路仿真時間必須保證ADC能夠每個周期輸出增加1位,也就是至少需要1 024個周期。圖7為輸入斜坡電壓后,得到的10個數字碼的輸出情況。緩變的斜坡電壓輸入會使得輸出每次按照遞變的順序變化,而從圖5~圖9中可以很明顯地看到任意相鄰的2個數字碼都是按照00-01-10-11的順序遞變。通過觀察所有的1 024個數字輸出碼,未發現任何誤碼和失碼的情況。

圖8所示為輸入信號為10 MHz(奈奎斯特頻率),采樣頻率100 MHz,采樣點數為4 096時的數字輸出經Matlab進行傅里葉變換的頻譜結果輸出,由圖可知,SNDR=58.4 dB,SFDR=79.6 dB,此時ENOB=9.5位。

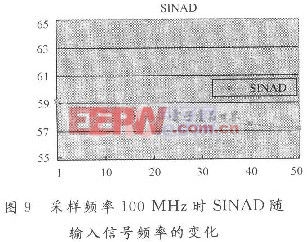

圖9所示為采樣頻率100MHz時SINAD隨輸入信號頻率的變化曲線。可見,在整個奈奎斯特頻率內,電路均能達到9位以上的有效精度。ADC各項性能參數如表2所示。

4 結語

本文設計了一個10位100 MHz的低功耗流水線ADC電路。該ADC采用了相鄰兩級共用一個運放的運放共享技術和逐級電容縮減技術來減小功耗和面積。在輸入頻率達到奈奎斯特頻率范圍內,整個ADC的有效位數始終高于9位。在100 MHz采樣頻率下,電路的功耗僅為45 mW。

評論