基于MRF24J40的IEEE802.15.4無(wú)線收發(fā)電路設(shè)計(jì)

IEEE802.15.4無(wú)線收發(fā)器MRF24J40芯片內(nèi)部包含有SPI接口、控制寄存器、MAC模塊、PHY驅(qū)動(dòng)器四個(gè)主要的功能模塊,支持IEEE802.15.4,MiWiTM,ZigBee等協(xié)議,工作在2.405~2.48 GHz ISM頻段,接收靈敏度為-91 dBm,最大輸入電平為+5 dBm,輸出功率為+0 dBm,功率控制范圍為38.75 dB,集成有20 MHz和32.768 kHz主控振蕩器,MAC/基帶部分采用硬件CSMA-CA結(jié)構(gòu),自動(dòng)ACK6和FCS檢測(cè),CTR、CCM和CBC-MAC模式采用硬件加密(AES-128),電源電壓范圍為2.4~3.6 V,接收模式電流消耗為18 mA,發(fā)射模式電流消耗為22 mA,睡眠模式電流消耗為2μA。

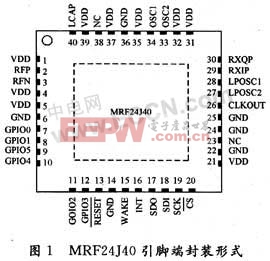

MRF24J40采用6 mm×6 mm QFN-40封裝,引腳端封裝形式如圖1所示。圖中:引腳端RFP和RFN分別為芯片的RF差分輸入/輸出正端和負(fù)端,兩者都是模擬輸入/輸出端口,與系統(tǒng)天線相連接;VDD為電源電壓輸入引腳端,每個(gè)電源電壓輸入引腳端都必須連接一個(gè)電源去耦電容;GND為接地引腳端,必須低阻抗的連接到電路的接地板;GPIOO~GPIO5是通用數(shù)字I/O口,其中GPIO0也被用來(lái)作為外部功率放大器使能控制,GPIO1和GPIO2也被用來(lái)作為外部TX/RX開關(guān)控制;RESET為復(fù)位引腳端,低電平有效;WAKE為外部喚醒觸發(fā)輸入端;INT為到微控制器的中斷引腳端;SDO,SDI,SCK和CS是MRF24J40的SPI接口輸入輸出引腳端,其中SDO是MRF24J40的串行數(shù)據(jù)輸出,SDI是MRF24J40的串行接口數(shù)據(jù)輸入,SCK是串行接口的時(shí)鐘,CS是串行接口使能控制引腳端;LPOSC1和LPOSC2為32 kHz晶振輸入正端和負(fù)端;OSC1和OSC2為20 MHz晶振輸入正端和負(fù)端;CLKOUT為20/10/5/2.5 MHz時(shí)鐘輸出端;LCAP引腳端用來(lái)連接一個(gè)180 pF的PLL環(huán)路濾波器電容;XIP和RXQP為接收I通道和Q通道輸出正端。

2 MRF24J40構(gòu)成的IEEE802.15.4無(wú)線收發(fā)電路

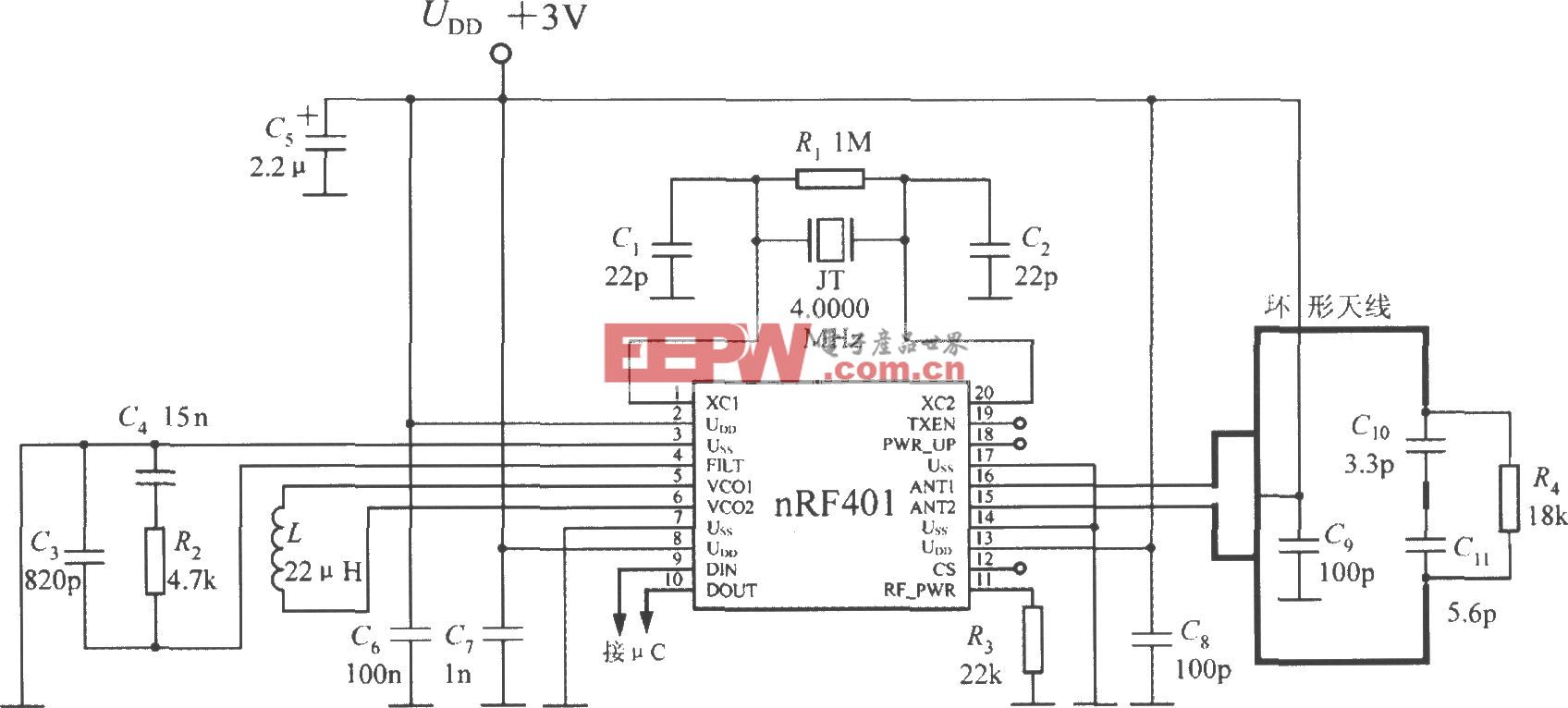

MRF24J40構(gòu)成的IEEE802.15.4無(wú)線收發(fā)電路如圖2所示,各電源電壓引腳端根據(jù)需要分別連接了27 pF,10 nF,100 nF,2.2μF去耦電容器。RF差分輸入/輸出正端RFP和負(fù)端RFN通過(guò)L3,L4,G37和C43組成平衡一不平衡變換電路,將MRF24J40的RF差分輸入/輸出形式轉(zhuǎn)換為單端輸入/輸出形式。L1,C23和C33構(gòu)成π型匹配電路,使平衡一不平衡變換電路阻抗與天線的阻抗相匹配。LPOSC1和LPOSC2引腳端連接32 kHz晶振和電容,構(gòu)成32 kHz時(shí)鐘振蕩器電路。OSC1和OSC2引腳端連接20 MHz晶振和電容,構(gòu)成20 MHz時(shí)鐘振蕩器電路。產(chǎn)生的時(shí)鐘信號(hào)作為芯片內(nèi)部時(shí)鐘信號(hào),并可以提供給外部的微控制器使用。

引腳端RESET,WAKE,INT,SDO,SDI,SCK,CS連接到微控制器,在微控制器的控制下完成數(shù)據(jù)的收發(fā)。

3印制電路板(PCB)設(shè)計(jì)

3.1 PCB設(shè)計(jì)基本要求

MRF24J40構(gòu)成的IEEE802.15.4無(wú)線收發(fā)電路工作頻率范圍為2.405~2.48 GHz,對(duì)PCB的設(shè)計(jì)有十分高的要求。PCB采用4層結(jié)構(gòu),如圖3所示,分別為信號(hào)層,RF接地層,電源布線層和接地層,采用FR4材料。

評(píng)論