高速電路傳輸線效應和信號完整性問題分析

隨著系統設計復雜性和集成度的大規模提高,電子系統設計師們正在從事100MHZ以上的電路設計,總線的工作頻率也已經達到或者超過50MHZ,有一大部分甚至超過100MHZ。目前約80% 的設計的時鐘頻率超過50MHz,將近50% 以上的設計主頻超過120MHz,有20%甚至超過500M。

本文引用地址:http://www.104case.com/article/180144.htm當系統工作在50MHz時,將產生傳輸線效應和信號的完整性問題;而當系統時鐘達到120MHz時,除非使用高速電路設計知識,否則基于傳統方法設計的PCB將無法工作。因此,高速電路信號質量仿真已經成為電子系統設計師必須采取的設計手段。只有通過高速電路仿真和先進的物理設計軟件,才能實現設計過程的可控性。

基于上述定義的傳輸線模型,歸納起來,傳輸線會對整個電路設計帶來以下效應。

· 反射信號Reflected signals

· 延時和時序錯誤Delay Timing errors

· 過沖(上沖/下沖)Overshoot/Undershoot

· 串擾Induced Noise (or crosstalk)

· 電磁輻射EMI radiation

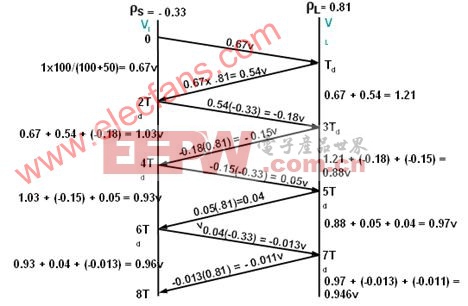

1 反射信號

在高速電路中,信號的傳輸如上圖所示,如果一根走線沒有被正確終結(終端匹配),那么來自于驅動端的信號脈沖在接收端被反射,從而引發不可預期效應,使信號輪廓失真。當失真變形非常顯著時可導致多種錯誤,引起設計失敗。同時,失真變形的信號對噪聲的敏感性增加了,也會引起設計失敗。如果上述情況沒有被足夠考慮,EMI將顯著增加,這就不單單影響自身設計結果,還會造成整個系統的失敗。

反射信號產生的主要原因:過長的走線;未被匹配終結的傳輸線,過量電容或電感以及阻抗失配。

2 延時和時序錯誤

信號延時和時序錯誤表現為:信號在邏輯電平的高與低門限之間變化時保持一段時間信號不跳變。過多的信號延時可能導致時序錯誤和器件功能的混亂。

通常在有多個接收端時會出現問題。電路設計師必須確定最壞情況下的時間延時以確保設計的正確性。信號延時產生的原因:驅動過載,走線過長。

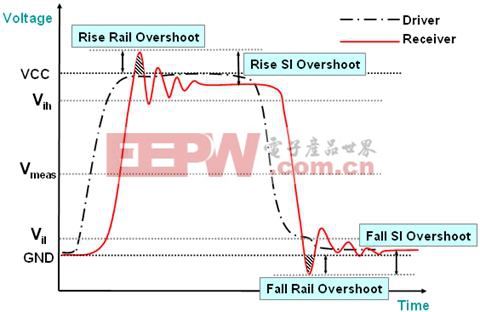

3 過沖

過沖來源于走線過長或者信號變化太快兩方面的原因。雖然大多數元件接收端有輸入保護二極管保護,但有時這些過沖電平會遠遠超過元件電源電壓范圍,損壞元器件。

4 串擾

串擾表現為在一根信號線上有信號通過時,在PCB板上與之相鄰的信號線上就會感應出相關的信號,我們稱之為串擾。

信號線距離地線越近,線間距越大,產生的串擾信號越小。異步信號和時鐘信號更容易產生串擾。因此解串擾的方法是移開發生串擾的信號或屏蔽被嚴重干擾的信號。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論