低功耗通用語音處理平臺的設(shè)計實現(xiàn)

HR/W:HPI讀寫信號線。標(biāo)識著MCU與DSP的通信方向。該信號線為高,表示MCU從DSP的存儲空間中讀取數(shù)據(jù);為低,表示MCU將數(shù)據(jù)寫入DSP的存儲空間。

HDS1/2:HPI數(shù)據(jù)控制信號。可以適應(yīng)不同類型的MCU的數(shù)據(jù)控制信號。要將HCNTL2置高,本例中的接法是HCNTL1通過MSP430F149的P2.1來控制。

HRDY:HPI準(zhǔn)備好信號。DSP通過該信號通知MCU當(dāng)前主機(jī)接口是否可以訪問。為低,DSP的主機(jī)接口忙,MCU不能通過它訪問;為高,可以訪問。

HCNTL0/1:HPI訪問控制信號。在復(fù)用模式中,通過這2個信號決定本次MCU訪問的是DSP的HPI接口的內(nèi)部寄存器。

HAS:HPI地址控制信號。在復(fù)用模式中,直接置高。

HMODE:HPI模式選擇信號。置高,HPI工作在非復(fù)用模式下;置低,HPI工作在復(fù)用模式下。

HINT:主機(jī)中斷信號。當(dāng)DSP將該信號線置低時,表示DSP請求主機(jī)中斷。因此這根信號線應(yīng)加上拉電阻。

HBE0/1:HPI字節(jié)使能信號。TMS320VC5510A中置低,忽略該信號。

MSP430F149通過向DSP主機(jī)接口內(nèi)部的3個寄存器寫入相應(yīng)的數(shù)據(jù)來控制相應(yīng)的通信方式。在復(fù)用方式下,這3個寄存器分別是 HPIC(控制寄存器)、HPIA(地址寄存器)、HPID(數(shù)據(jù)寄存器)。為了提高在復(fù)用方式下的訪問速度,DSP的HPI接口還提供了另外一個數(shù)據(jù)寄存器。當(dāng)MCU訪問連續(xù)地址時,可以通過HCNTL0/1選擇利用這個數(shù)據(jù)寄存器進(jìn)行連續(xù)訪問DSP內(nèi)部存儲器,相應(yīng)的地址寄存器會在每次訪問這個數(shù)據(jù)寄存器之后自動增加。

MCU和DSP的通信通過中斷完成。其中MSP430F149通過訪問HPIC寄存器,將其中的DSPINT位置1來觸發(fā)DSP的中斷,而DSP則通過將HINT信號線置低來觸發(fā)MCU的中斷。

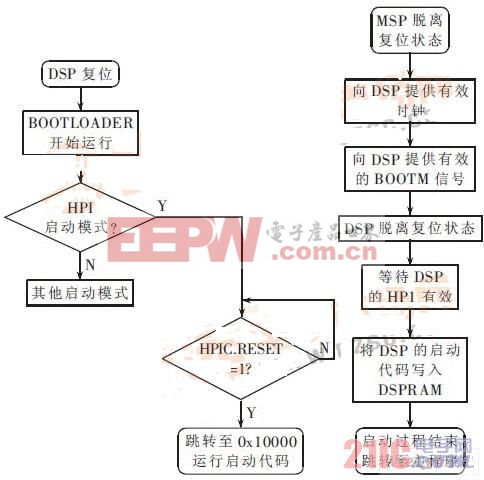

當(dāng)前的硬件平臺中,通過置I/O口線的方式實現(xiàn)了MCU對DSP主機(jī)接口的讀寫操作,可以選擇通過主機(jī)啟動DSP的方式[4]。啟動過程的框圖如圖6所示。

HPI 啟動方式流程圖

圖6 HPI 啟動方式流程圖

3 系統(tǒng)軟件優(yōu)化降低功耗

上面已提到,在硬件平臺的設(shè)計中采用了低功耗的器件,屬于低功耗設(shè)計中的靜態(tài)技術(shù)。在系統(tǒng)軟件的具體實現(xiàn)中,可以根據(jù)執(zhí)行算法的情況進(jìn)行動態(tài)調(diào)整,從而達(dá)到降低系統(tǒng)功耗的目的。由于DSP采用內(nèi)部可編程鎖相環(huán)(PLL)產(chǎn)生時鐘,可以使處理器根據(jù)對于計算能力的即時需求動態(tài)改變運行速度。雖然系統(tǒng)提供了幾種低功耗模式,但是相應(yīng)的喚醒時間各不相同,實際中要根據(jù)具體情況對功耗和喚醒時間綜合考慮。

由于MCU具有較強(qiáng)的事件響應(yīng)能力以及DSP具有較強(qiáng)的數(shù)據(jù)處理能力,因此可以通過MCU針對不同算法動態(tài)地改變系統(tǒng)的工作頻率及DSP的工作狀態(tài),從而降低系統(tǒng)功耗。例如在該平臺運行清華大學(xué)自主研制的600、1 200、2 400bps語音算法,需要針對不同算法要求不同的數(shù)據(jù)運算量進(jìn)行動態(tài)配置。DSP采用MCU提供的8.192MHz的時鐘、通過片內(nèi)集成的DPLL進(jìn)行倍頻得到所需要的主時鐘。由于系統(tǒng)的部分代碼是處于54兼容模式下,所以在系統(tǒng)軟件的主函數(shù)中,當(dāng)不需要進(jìn)行編解碼操作時,系統(tǒng)可以處于正常狀態(tài),即IDLE1或IDLE2狀態(tài)。更具體的管理可以使用c55x系列的IDLE domain(IDLE域)機(jī)制進(jìn)行管理[6]。3種狀態(tài)具體描述如下:

NO IDLE:定時器、通用串口和內(nèi)核均處于正常工作模式。

IDLE 1:定時器和通用串口正常工作模式,內(nèi)核處于IDLE狀態(tài),由中斷喚醒。

IDLE 2:定時器、通用串口和內(nèi)核都處于IDLE狀態(tài),由中斷喚醒。

針對不同的算法,由于要求的數(shù)據(jù)運算量不同,能夠保證算法工作的最低系統(tǒng)頻率也不同。通過對不同的數(shù)據(jù)運算要求動態(tài)調(diào)整系統(tǒng)的工作狀態(tài),可以最大限度地實現(xiàn)降低功耗的目的,從而實現(xiàn)針對不同運算量的功耗控制。實際使用中,當(dāng)DSP:運行600SELP算法時,系統(tǒng)工作在32.768MHz;運行1 200SELP算法時,系統(tǒng)工作在40.960MHz;運行2 400SELP算法時,系統(tǒng)工作在24.576MHz。與單一的運行在81.92MHz情況下相比,系統(tǒng)功耗分別降低了41%、36%、48%,大大減少了系統(tǒng)功耗。

該硬件平臺已經(jīng)成功運行了G.723.1、G.729A/B和CVSD等算法,并且獲得了良好的效果,具有廣闊的應(yīng)用前景。本文引用地址:http://www.104case.com/article/179973.htm

評論