寄存器傳輸級的低功耗設計方法

其中,PTurn是開關電流ITurn產生的動態功耗;Pshort是動態情況下P管和N管同時導通時的短路電流Ishort產生的動態功耗;而Pleakage 是由擴散區和襯底之間的反向偏置漏電流Ileakage產生的靜態功耗。如圖1所示。本文引用地址:http://www.104case.com/article/179809.htm

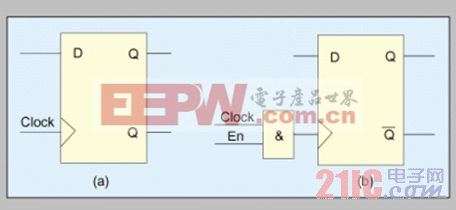

圖2a:傳統的設計。圖2b:增加了門控時鐘的設計。

在這三項中PTurn大約占電路功耗的80% ,因而這里就只考慮開關電流ITurn所產生的動態功耗PTurn。ITurn是這樣產生的:在CMOS電路,當輸入為“0”時,PMOS導通,電源通過PMOS向負載電容充電;而當電路輸入為“1” 時,負載電容又會通過NMOS向地放電。ITurn就是不斷對負載電容充放電所產生的開關電流。

一個CMOS反相器由開關電流引起的平均動態功耗是:PTurn=CLVDD2f

其中,CL是負載電容,VDD是電路的電壓,f是時鐘頻率。所以,要想降低電路的功耗就應該降低電路的電壓和頻率。

寄存器傳輸級的低功耗設計

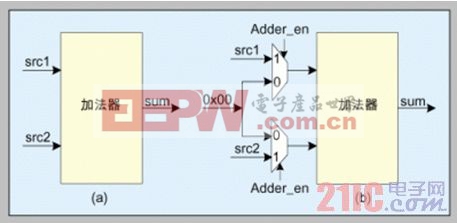

圖3a:最基本的加法器設計。圖3b:采用操作數隔離方法設計的加法器。

寄存器傳輸級的低功耗設計方法有很多種,本文只列舉三種最為常用的設計方法:門時鐘、操作數隔離及存儲器分區訪問。

1.門控時鐘

從上面的討論知道,CMOS電路的功耗是和頻率有著密切關系的,因此動態的關閉處于空閑狀態的時鐘具有明顯的節電效果。

圖2a是傳統的設計:系統的時鐘直接接到D觸發器的時鐘輸入端,不管什么情況,只要輸入的Clock翻轉,觸發器就會工作,整個系統也一直不斷的運行。而圖2b是增加了門控時鐘的設計:當系統正常工作時,譯碼出來的En信號為高,則觸發器可以正常鎖存數據;當系統處于空閑狀態時,把En信號清零,這樣,由于給觸發器的Clock一直保持零,不會發生翻轉,所以觸發器不會鎖存新的數據,整個系統被掛起,系統將進入低功耗模式。

在電路中加入門控時鐘很容易,可以用Verilog直接在描述中加入,也可以通過Synopsys的工具PowerCompile自動加入。通過加入門控時鐘,系統可以有選擇的停止不相關模塊的時鐘,以最大程度的節省動態功耗。

2.操作數隔離

這種方法主要是對系統中的算術、邏輯運算模塊進行低功耗設計,其主要思想就是:在不進行算術、邏輯運算的時候,使這些模塊的輸入保持“0”,不讓操作數進來,輸出結果不會翻轉;而如果進行這方面的運算時,再將它們打開。

評論