高速CMOS鐘控比較器的設計

2. 2 失調電壓

比較器的失調電壓主要來源于預運放的失調電壓。它主要是由MOS管閾值電壓的失配和電流的失配引起的,它的標準差如下式:

其中:

式中,δ21, 2是預運放輸入差分對失調電壓的標準差,δ23, 5是預運放負載管失凋電壓的標準差; AVTN , AVTP ,AβN , AβP分別是NMOS管和PMOS管工藝模型中閾值電壓的失配因子和電流的失配因子。從式( 6) 、(7) 、(8)可以看出,減小預運放輸入差分對管和負載管的過驅動電壓,并適當增加它們的面積可有效地減小輸入失調電壓。但同時增大了漏極電容,降低比較器的速度。因此,比較器的設計需要在功耗、速度和精度之間進行折中。

3 電路仿真

通過以上分析,使用Hsp ice進行仿真與優化,最終確定比較器的核心電路(預運放與判斷級電路)內各晶體管尺寸如表1所示。

表1 比較器核心電路各晶體管的寬長比

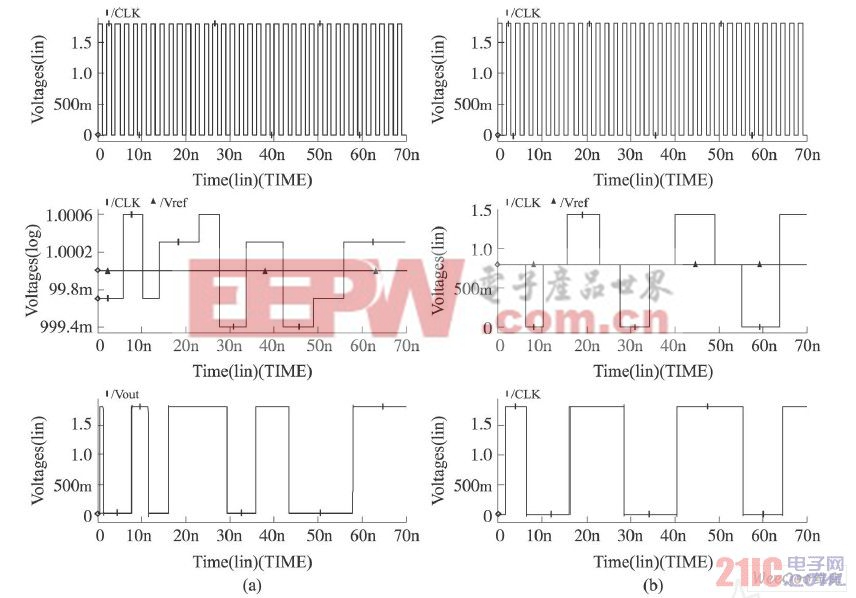

在電源電壓1. 8 V、SM IC 0. 18μm CMOS工藝模型下,采用Hsp ice對前面設計的比較器電路進行仿真。為了檢驗比較器在各種工作情況下輸出的正確性,在比較器的輸入端加上幅度和極性隨時間變化的信號作為測試信號,工作時鐘頻率為500MHz,仿真波形如圖6所示。圖6 ( a) 、( b)中第一欄是時鐘控制信號CLK,第2欄是輸入信號Vin和參考電壓Vref ,第三欄是比較器的輸出信號Vout。通過對仿真結果進行分析,在輸入信號為具有大跳變極端信號(在基準參考電壓0. 8 V 下,兩信號為0. 81、0 V或是0. 79、1. 8 V)的情況下,比較器的最小精度為±0. 3 mV (基準電壓1 V) ,仿真結果驗證了比較器功能的正確性。

圖6 比較器整體仿真波形

4 結論

本文設計了一個基于1. 8 V電源電壓、時鐘頻率可以達到500MHz的高速鐘控電壓比較器,采用預放大級、判斷級、輸出緩沖級結構,每一級的電路結構簡單,通過對各個部分電路的特點進行分析,優化了前置放大器的晶體管的尺寸,實現了高速、高精度、低功耗的要求。在SMIC 0. 18μm CMOS工藝模型下,采用Hspice對電路進行仿真,結果表明在500 MHz的時鐘頻率下,比較精度可達0. 3 mV,功耗僅為26. 6μW,該電路可以應用在高速Flash ADC電路中。

評論