一種大動態范圍的實時數控AGC電路的設計

3 設計與實現

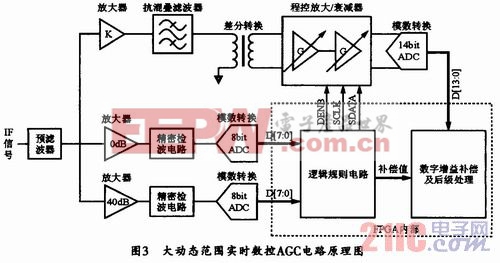

圖3所示是一種應用于數字中頻接收機的大動態范圍實時數控AGC電路的原理框圖。本文引用地址:http://www.104case.com/article/179307.htm

射頻信號經前端混頻處理后可輸出21.4 MHz的模擬中頻信號,該中頻信號的功率電平范圍為-80 dBm~20 dBm。經過預選濾波器,該中頻信號將分別被送入到抗混疊濾波電路和信號幅度提取電路。設計中,在對信號進行幅度提取前,應先對信號進行不同增益的放大,增益分別為0 dB和40 dB,經放大后的信號可送入峰值包絡檢波器中得到幅度值,從而完成信號幅度的提取。之后,可用分辨率比較低的ADC器件對幅度值進行量化,當輸入信號比較大時,可根據0dB通道的量化值得到檔位信息;而當輸入信號比較小時,則可根據40 dB通道的量化值得到檔位信息。因此,根據不同增益通道的量化值來判斷檔位信息的方法極大地豐富了檔位信息,進而精確地實現數控增益放大/衰減。

設計可選用AD公司推出的線性數控增益放大/衰減芯片AD8369,并采用兩片數控芯片級聯的方式對輸入信號進行實時放大/衰減,共可得到90 dB的增益調節范圍。邏輯規則產生模塊可同時控制兩片數控增益放大/衰減芯片,以使增益平均分配在兩級數控增益放大/衰減芯片上,從而實現增益的粗調和細調。設計時可選用AD公司的14位ADC器件ADS6145來對模擬信號進行量化。

由于ADS6145轉換時的參考電壓為1 V,故應將該輸入信號幅度值盡可能的放大/衰減到略小于1 Vpp。本設計中的具體操作是將每一檔位中的最大輸入信號功率放大/衰減到12 dBm,這樣可以保證ADC工作在最佳狀態,以使輸出有效位最大。根據以上設計原則,便可以得到具體的分檔信息及表1所列的對應放大/衰減量表。

4 結束語

本文采用前饋式電路結構,并利用抗混疊電路的延遲特性實現了對輸入信號的實時放大/衰減。同時利用FPGA器件良好的數字特性實現了數控AGC的設計,從而實現了對信號的實時數字增益補償,有效減少了電路體積。同時,采用兩級數控增益放大/衰減器級聯和根據兩路不同增益通道提取的幅度值來判斷檔位信息,也提高了實時數控AGC電路的動態范圍和整個系統的精度。實驗結果表明,該電路能夠實現實時AGC的電路功能,并有效擴展了動態范圍。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論