一種大動(dòng)態(tài)范圍的實(shí)時(shí)數(shù)控AGC電路的設(shè)計(jì)

2 實(shí)時(shí)AGC電路的關(guān)鍵技術(shù)

實(shí)現(xiàn)實(shí)時(shí)AGC電路的關(guān)鍵在于抗混疊濾波器的設(shè)計(jì)、邏輯規(guī)則產(chǎn)生模塊的設(shè)計(jì)和數(shù)字增益補(bǔ)償模塊的設(shè)計(jì)。

設(shè)計(jì)中,AGC的實(shí)時(shí)性體現(xiàn)在兩個(gè)方面,首先是對(duì)輸入信號(hào)的實(shí)時(shí)放大/衰減,設(shè)計(jì)可采用前饋式電路結(jié)構(gòu),并將信號(hào)分為兩路進(jìn)行處理,通常需要在放大-抗混疊濾波電路的延遲時(shí)間段內(nèi)完成對(duì)信號(hào)的檔位信息判斷及控制自動(dòng)增益放大/衰減芯片增益的改變,從而實(shí)現(xiàn)對(duì)輸入信號(hào)的實(shí)時(shí)放大/衰減;其次是利用數(shù)字電路對(duì)數(shù)據(jù)后處理的能力來(lái)實(shí)時(shí)完成數(shù)字增益補(bǔ)償。

對(duì)于前者,其關(guān)鍵在于抗混疊濾波器的設(shè)計(jì)。抗混疊濾波器的作用有二,其一是濾除帶外信號(hào),防止頻譜混疊;其二是產(chǎn)生一定時(shí)間的延遲。一般將抗混疊濾波器設(shè)計(jì)成低通或者帶通濾波器,并采用模擬器件電感和電容搭建而成,這樣就會(huì)產(chǎn)生固定時(shí)間的延遲。要實(shí)現(xiàn)對(duì)輸入信號(hào)的實(shí)時(shí)放大/衰減,就要精心設(shè)計(jì)并利用這個(gè)延遲時(shí)間,在延遲時(shí)間內(nèi)同步地完成一系列檢測(cè)、控制及計(jì)算工作,包括用信號(hào)幅度提取電路得到輸入信號(hào)的包絡(luò)電平功率,用邏輯規(guī)則產(chǎn)生模塊并通過(guò)包絡(luò)電平功率的量化值判斷出檔位信息,再根據(jù)檔位信息生成各個(gè)檔位的電壓增益值,同時(shí)配置數(shù)控增益放大/衰減器對(duì)信號(hào)進(jìn)行放大/衰減。

而對(duì)于后者,其關(guān)鍵在于數(shù)字增益補(bǔ)償模塊的設(shè)計(jì)。當(dāng)邏輯規(guī)則產(chǎn)生模塊生成檔位信息后,可根據(jù)檔位信息計(jì)算出每一個(gè)檔位的補(bǔ)償值,然后將其送入數(shù)字增益補(bǔ)償模塊。數(shù)字增益補(bǔ)償模塊利用該補(bǔ)償值對(duì)ADC轉(zhuǎn)換后的結(jié)果進(jìn)行補(bǔ)償,從而得到輸入信號(hào)的幅度值。流水線型ADC器件轉(zhuǎn)換操作存在的固定延遲時(shí)間一般為采樣周期的固定倍數(shù),所以,在數(shù)字增益補(bǔ)償時(shí),不能出現(xiàn)對(duì)信號(hào)的誤補(bǔ)償,以防止補(bǔ)償后的信號(hào)發(fā)生畸變,因而要求時(shí)間同步。在數(shù)字邏輯中,時(shí)間同步或延遲的控制較容易實(shí)現(xiàn),可用D觸發(fā)器或者計(jì)數(shù)器來(lái)實(shí)現(xiàn)延遲,這樣延遲時(shí)間也容易控制。

要得到輸入信號(hào)的準(zhǔn)確幅度值,在數(shù)字增益補(bǔ)償模塊中僅采用移位是不行的,還需要在移位的基礎(chǔ)上進(jìn)行校準(zhǔn),其原因有兩條,第一:由于在前端電路中模擬器件固有缺陷的存在導(dǎo)致了中頻信號(hào)在經(jīng)過(guò)調(diào)理電路后存在一定的電平誤差,因此,在數(shù)字增益補(bǔ)償時(shí),需要校準(zhǔn)這個(gè)誤差;第二:對(duì)數(shù)字信號(hào)左移/右移一位,相應(yīng)的功率電平將放大/衰減6 dB。所以,移位只能實(shí)現(xiàn)6 dB整數(shù)倍增益的補(bǔ)償,而不能實(shí)現(xiàn)其它增益值的補(bǔ)償。此外,在加入自動(dòng)增益放大/衰減后,系統(tǒng)動(dòng)態(tài)范圍將增加,故需要考慮信號(hào)表征的問(wèn)題,通過(guò)對(duì)ADC轉(zhuǎn)換后的數(shù)據(jù)進(jìn)行位擴(kuò)展能有效地解決這個(gè)問(wèn)題。

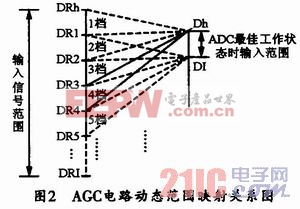

在整個(gè)實(shí)時(shí)AGC電路中,邏輯規(guī)則產(chǎn)生模塊將起到紐帶作用,它是電路的控制核心,因此,采用數(shù)字電路實(shí)現(xiàn)可對(duì)其他電路進(jìn)行控制。根據(jù)包絡(luò)幅度量化值,該模塊可產(chǎn)生檔位信息并計(jì)算出每一檔位的放大/衰減增益值和補(bǔ)償值,同時(shí)配置數(shù)控增益放大/衰減器以調(diào)節(jié)增益,同時(shí)提供補(bǔ)償值至數(shù)字增益補(bǔ)償模塊。AGC電路對(duì)信號(hào)進(jìn)行放大/衰減實(shí)質(zhì)上是對(duì)信號(hào)的動(dòng)態(tài)范圍進(jìn)行某種“映射”。根據(jù)輸入信號(hào)的大小可將其劃分為不同的檔位,自動(dòng)增益控制的作用是將不同檔位的信號(hào)加以放大/衰減,并將各檔輸入信號(hào)范圍均“映射”到ADC器件最佳工作范圍內(nèi),其映射關(guān)系如圖2所示。在對(duì)信號(hào)進(jìn)行分檔時(shí),要考慮“映射”后的信號(hào)范圍應(yīng)匹配ADC器件信號(hào)的輸入范圍,所以,分檔不宜選擇過(guò)少,并且,同一檔位信號(hào)大小也不能相差太大,以防止“映射”后的信號(hào)落在ADC最佳工作范圍之外。本文引用地址:http://www.104case.com/article/179307.htm

圖2中,DRh,DR1,DR2,DR3,DR4,DR5和DR1是分別對(duì)應(yīng)不同輸入信號(hào)的功率電平值,Dh和D1對(duì)應(yīng)ADC器件最佳工作范圍的最大和最小功率電平值。

DIY機(jī)械鍵盤(pán)相關(guān)社區(qū):機(jī)械鍵盤(pán)DIY

評(píng)論