一種低壓高線性CMOS模擬乘法器設(shè)計(jì)

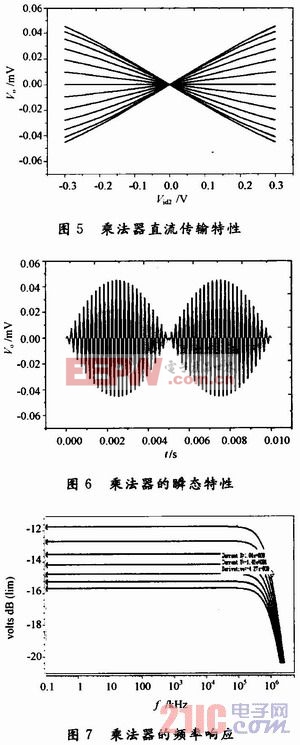

如圖5所示:Vid1=±0.3 V,Vid2的輸入范圍也是-0.3~+0.3 V,且以50 mV的步長變化。可以看到對(duì)于整個(gè)輸入動(dòng)態(tài)范圍,電路保持很好的線性度。本文引用地址:http://www.104case.com/article/179291.htm

圖6所示該乘法器用作調(diào)幅電路。在Vid1端輸入一個(gè)幅值0.3 V,頻率5 kHz的正弦載波信號(hào),Vid2端輸入一個(gè)同樣幅值,頻率100 MHz的正弦調(diào)制信號(hào),得到一個(gè)完整的正弦包絡(luò)。

如圖7所示:固定V2,V3,V4輸入不變,對(duì)V1以0.05 V步長進(jìn)行DC掃描,掃描范圍0.45~0.75 V。得到的-3 dB帶寬為1 GHz。可見,圖4所示乘法器頻率特性良好,帶寬較寬,可以處理較高頻率信號(hào)。

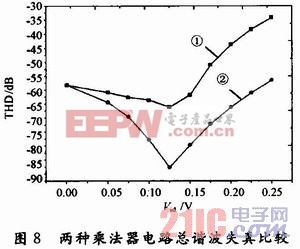

圖8是該乘法器電路THD仿真結(jié)果;圖4中在Vid2加上頻率100 kHz,幅度變化的正弦信號(hào),Vid1固定在0.6 V;圖1中在Vid2加上頻率100 kHz相同幅度變化的正弦信號(hào),Vid1固定在0.6 V,圖中折線①代表圖1乘法器的仿真結(jié)果,折線②代表圖4乘法器的仿真結(jié)果,可以明顯看出,對(duì)于同樣的輸入,圖4所示乘法器失真更小,線性度更好。整體來說,本乘法器較好的完成了對(duì)模擬信號(hào)的相乘處理功能,在整個(gè)線性輸入范圍內(nèi)都表現(xiàn)出完好的線性相乘結(jié)果,較高的線性度以及較大的-3 dB帶寬,并經(jīng)仿真驗(yàn)證成功,可能存在的不足之處在于其線性輸入范圍有待進(jìn)一步提高。

3 版圖設(shè)計(jì)

使用0.18 μm CMOS工藝技術(shù),對(duì)圖4電路設(shè)計(jì)版圖。與一般的低壓CMOS四象限模擬乘法器電路(圖1)相比,版圖設(shè)計(jì)時(shí)最顯著的提升就是節(jié)約4個(gè)電阻的版圖面積,如果工藝中包含高阻值的電阻類型,這種優(yōu)勢(shì)就更為突出。

4 結(jié)語

本文提出了一種結(jié)構(gòu)簡單的高線性CMOS四象限模擬乘法器,該乘法器基于交叉耦合平方電路結(jié)構(gòu)并采用減法電路來實(shí)現(xiàn)。HSPICE仿真結(jié)果顯示,該乘法器功耗可低至80μW,其線性輸入范圍達(dá)到±0.3 V,-3 dB帶寬可達(dá)到1 GHz。在同樣的電源電壓和功耗條件下,相比于圖1所示的乘法器,最突出的優(yōu)點(diǎn)是線性度得到顯著改善。在要求低高線性的高頻模擬信號(hào)處理系統(tǒng)中該乘法器有望得到廣泛應(yīng)用。

評(píng)論