新型磁耦合隔離電路設計

3.1.3 初級驅動單元的功能仿真

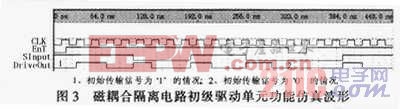

使用QuartusII 9.0對磁耦合隔離電路初級驅動單元進行功能仿真,得到功能仿真曲線如圖3所示。本文引用地址:http://www.104case.com/article/179136.htm

從上圖看出,在1的位置后,雖然沒有輸入信號(SInput)的變化,輸出驅動波形中也產生了一個驅動脈沖,這就是為了保證在輸入信號初始值為高電平時保持輸入和輸出的一致,由電路自動加入的;在位置2,復位后次級接收電路初始態已經為低電平,輸入信號的初始值也為低電平,隔離輸入輸出一致,故不需要自動加入驅動脈沖。

3.2 次級接收模塊的實現

Receive構成磁耦合隔離電路的次綴接收模塊,該模塊完成的功能為:在復位信號到來后,接收電路復位輸出為‘0’,而后每接收到一個脈沖,輸出反轉一次。由于復位后接收模塊的初始態已與初級輸入信號的初始值一致,初級輸入信號每發生一次跳變,初級驅動電路輸出一個脈沖,因此在任何時刻,次級接收電路的輸出都與初級輸入信號一致。從而實現低頻或直流信號的磁耦合隔離傳輸。該模塊實際上就是一個帶復位功能的一位計數器,關于它的VHDL實現在參考文獻中有現成的例子,此處不再贅述。

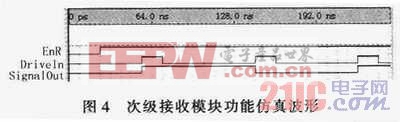

InputS模塊的功能仿真波形如圖4所示。

3.3 模塊工作頻率的說明

一般來說,對于上升沿持續時間在50ns左右脈沖變壓器,傳輸信號跳變沿驅動脈沖的寬度至少應大于此時間,在本設計中,選用60 ns的脈沖作為傳輸信號跳變沿驅動脈沖的寬度,為了使兩個相鄰的傳輸信號跳變沿驅動脈沖能夠被接收模塊準確識別,它們之間應至少間隔一個脈沖寬度的時間,這樣算起來,傳輸信號的最短持續時間應為120ns,而對于直流信號上述模塊也能準確傳輸(原理前面已經述及),因此該模塊傳輸信號的頻率范圍是0~8 MHz。對于高于8 MHz的數字信號,模塊將不能正確工作。

上述分析是在脈沖變壓器上升沿為50ns的前提下給出的,如果上升沿時間再短些,模塊的工作頻率上限還可提高。

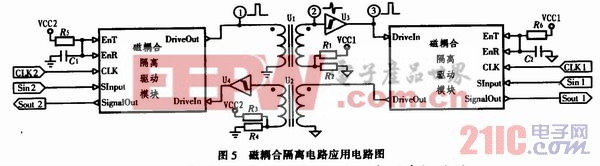

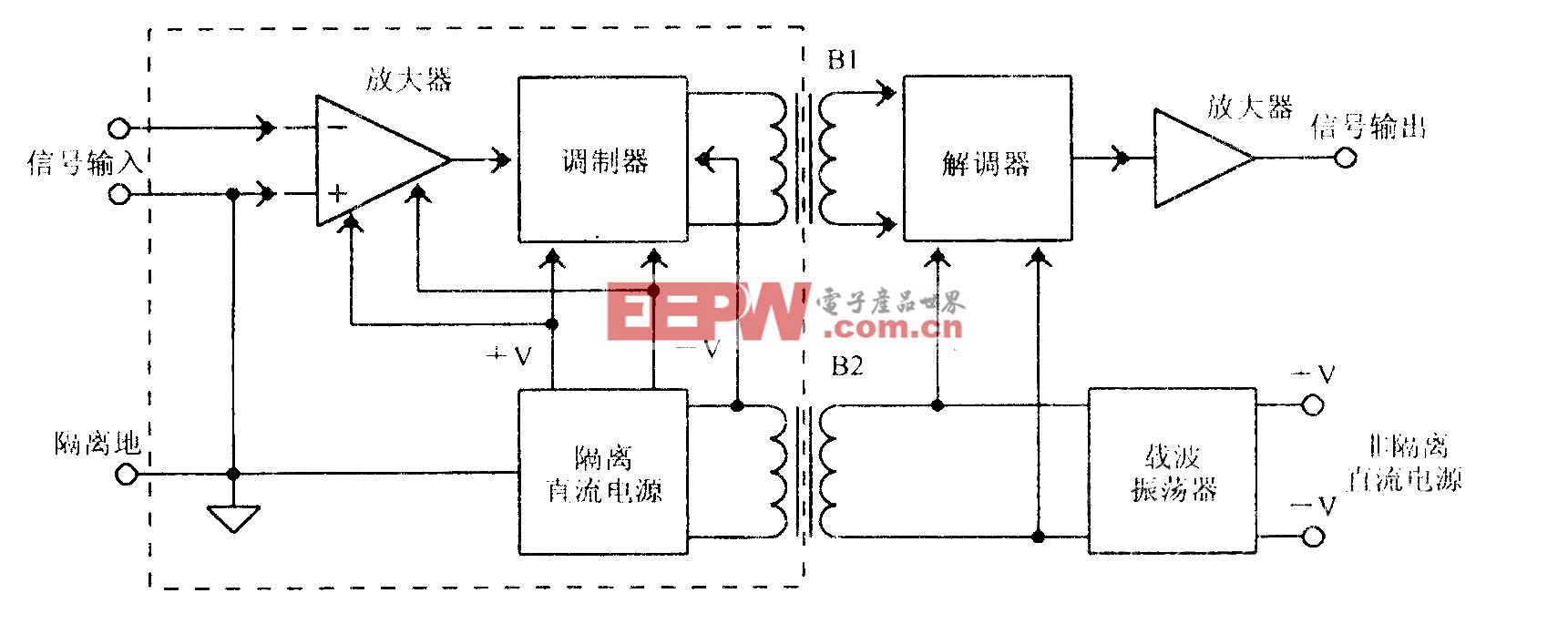

3.4 新受磁耦合隔離電路應用

新型磁耦合隔離模塊的應用電路如圖5所示,該電路用于完成信號Sin1到Sour2,Sin2到Sout1的磁耦合隔離傳輸。在電路中,U1、U2為脈沖變壓器ITNA-0235-D103,上升沿持續時間50 ns;U3、U4為Schmitt觸發器,用于將脈沖變壓器輸出的信號整形成脈沖信號,測試點①② ③的信號波形如圖前面中所示。R5、C1和R6、C2分別組成兩個磁耦合隔離驅動模塊的上電復位電路,兩個復位電路的時間常數應設計在10μs左右,以保證模塊穩定復位;R1、R2和R3、R4分別組成兩個電平移動電路,用于將脈沖變壓器輸出的交流信號移動到0~VCC的范圍。在模塊配置到CPLD時DriveOut引腳必須配置成ITL模式以增加電流驅動能力。電路在實際使用時,EnT與EnR可以改成由邏輯信號直接控制,這樣就可以使驅動模塊穩定時間可控,在由于受到干擾而使電路出現錯誤時,可以通過施加EnT與EnR信號使電路恢復正常工作。

對上述電路測試,得到如下測試結果:

1)電路能夠準確傳輸直流信號;

2)對小于8 MHz的數字信號跳變沿的傳輸延遲小于50 ns,對于8 MHz以上的數字信號上述電路不能工作;

3)電路功耗,由于用于信號傳輸驅動的邏輯電路只占CPLD的很小部分(在應用電路中,CPLD選用EPM240TC100,使用16個邏輯單元,占總邏輯單元數的7%,其他單元用作別的用途),準確功耗很難測量,但是在傳輸直流信號時磁耦合隔離部分的功耗與光隔的功耗對比就足以說明問題。傳輸高電平時,光隔電路需要持續消耗10 mA的電流,以維持穩定輸出高電平;而上述磁耦合隔離電路則只需要在最初的40 ns內消耗電流,其他時間磁耦合隔離部分消耗的電流為0,因此傳輸直流信號時,上述電路的功耗要遠小于光隔電路。

4 結論

該設計的創新點在于:1)以窄脈沖表示傳輸信號的狀態改變;2)以窄脈沖的磁耦合隔離傳輸代替輸入信號的隔離傳輸,降低隔離電路的功耗;3)實現低頻和直流信號的磁耦合隔離傳輸;4)驅動電路簡單,接收和發送模塊共需要16個邏輯單元就可實現上述功能;5)信號傳輸延遲很小。

存在的問題:1)傳輸信號的上限頻率受限,只能傳輸0~8 MHz的方波信號;2)在電路上電到復位信號結束的一段時間(10μs以內),電路不能正確傳輸信號,必須保證在此時間段內傳輸信號狀態穩定,否則后面的信號將全部錯誤。

總之,正是由于該設計具有電路簡單、功耗小、能夠實現磁耦合隔離傳輸低頻信號,且信號傳輸延遲很小等特點,拓展了磁耦合隔離技術的應用領域。

評論