應用于負電源的電平位移電路及器件設計

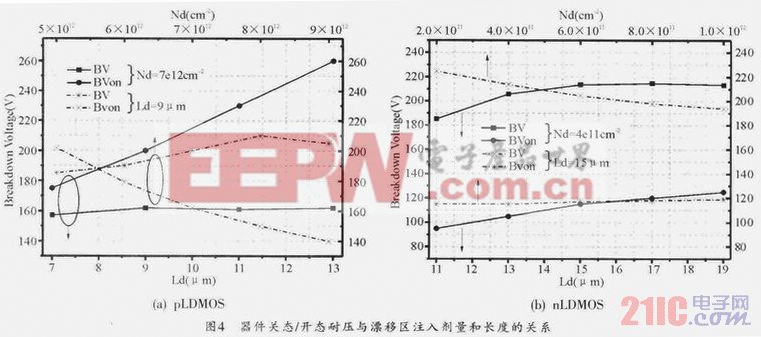

利用工藝器件聯合仿真,在傳統的正電源應用的LDMOS基礎上對器件的結構參數進行優化設計。圖4(a)為pLDMOS在漂移區注入劑量Nd=7 e12cm-2時關態耐壓、開態耐壓與漂移區長度Ld(μm)的關系,以及在漂移區長度Ld=9μm情況下關態耐壓、開態耐壓與漂移區注入劑量Nd(cm-2)的關系。其他參數為:n型體區注入劑量5e12 cm-2,Nsink注入劑量3e15 cm-2,P-buffer注入劑量1.5e13 cm-2,溝道長度3μm,柵極場板3μm。從仿真結果可以看出:pLDMOS的關態耐壓隨漂移區的增加而增大,隨漂移區的注入劑量的增大先增大后減小;開態耐壓隨著漂移區注入劑量的增大而降低,但是在一定范圍內漂移區長度對其影響較小。總體上,pLDMOS的關態耐壓、開態耐壓都在160V以上,完全能夠滿足8~-100V工作電壓(108V耐壓)的要求。本文引用地址:http://www.104case.com/article/178713.htm

圖4 (b)為nLDMOS在漂移區注入劑量Nd=4e11cm-2時關態耐壓、開態耐壓與漂移區長度Ld(μm)的關系,以及在漂移區長度Ld=15μm情況下關態耐壓、開態耐壓與漂移區注入劑量Nd(cm-2)的關系。其他參數為:p型體區注入劑量5e13 cm-2,Psink注入劑量3e15 cm-2,N-buffer注入劑量1e13cm-2,溝道長度3μm,柵極場板3.5μm。相對于pLDMOS,漂移區注入劑量和漂移區長度對于開態耐壓、關態耐壓的影響不大。同時關態耐壓都能維持在180V以上,但是開態耐壓卻只有90~120V,不能滿足8~100V工作電壓(108V耐壓)的要求。nLDMOS開態耐壓問題成為電路、器件設計的關鍵。

針對nLDMOS器件開態耐壓低的問題,有針對性地仿真了溝道長度、多晶硅柵場板長度及體區濃度對開態耐壓的影響。圖5(a)為nLDMOS的關態耐壓、開態耐壓及閾值與溝道長度(Lch)的關系。可以看出溝道長度對器件的開態耐壓和關態耐壓影響很小。閾值隨著溝道長度的增加而增加,這是由于采用橫向雙擴散形成溝道,所以隨著溝道長度增加,p型體區的濃度越來越大,閾值也就越來越大。圖5(b)為nLDMOS的關態耐壓、開態耐壓及閾值與多晶硅柵極場板長度(LPgate)的關系。在柵極場板較長時,其對閾值和關態耐壓影響很小,當柵極場板縮短到多晶硅柵不能覆蓋溝道時,器件的開態耐壓大幅增加。這時閾值也迅速增加。雖然多晶硅柵不能完全覆蓋溝道,但是由于開態時nLDMOS的柵漏電壓差很大,所以仍然能夠在表面形成反型層溝道。因此,大幅減短柵極場板能有效提高器件的開態耐壓,但是同時也帶來了器件不能有效開啟的問題。圖5(c)為nLDMOS的關態耐壓、開態耐壓及閾值與體區注入劑量(Pbody)的關系。可以看出增加體區的注入劑量對器件的耐壓影響很小。但是隨著注入劑量的增加,體區濃度增加,所以閾值就增加,同時器件的開態耐壓也隨之增加。當體區注入劑量達到5e14cm-2時,閾值增加緩慢,開態耐壓卻大幅增加,所以只能通過閾值上的犧牲來改善nLDMOS的開態擊穿耐壓。

DIY機械鍵盤相關社區:機械鍵盤DIY

評論