最大消耗380nA電流的電壓基準(zhǔn)源設(shè)計(jì)

則流過(guò)電阻R1的電流為:

由式(3)可以看出,電流IR只與晶體管寬長(zhǎng)比,電阻R1,斜率因子n;波爾滋曼常數(shù)k,絕對(duì)溫度T有關(guān),與電源電壓無(wú)關(guān),是與溫度成正比的PTAT電流。

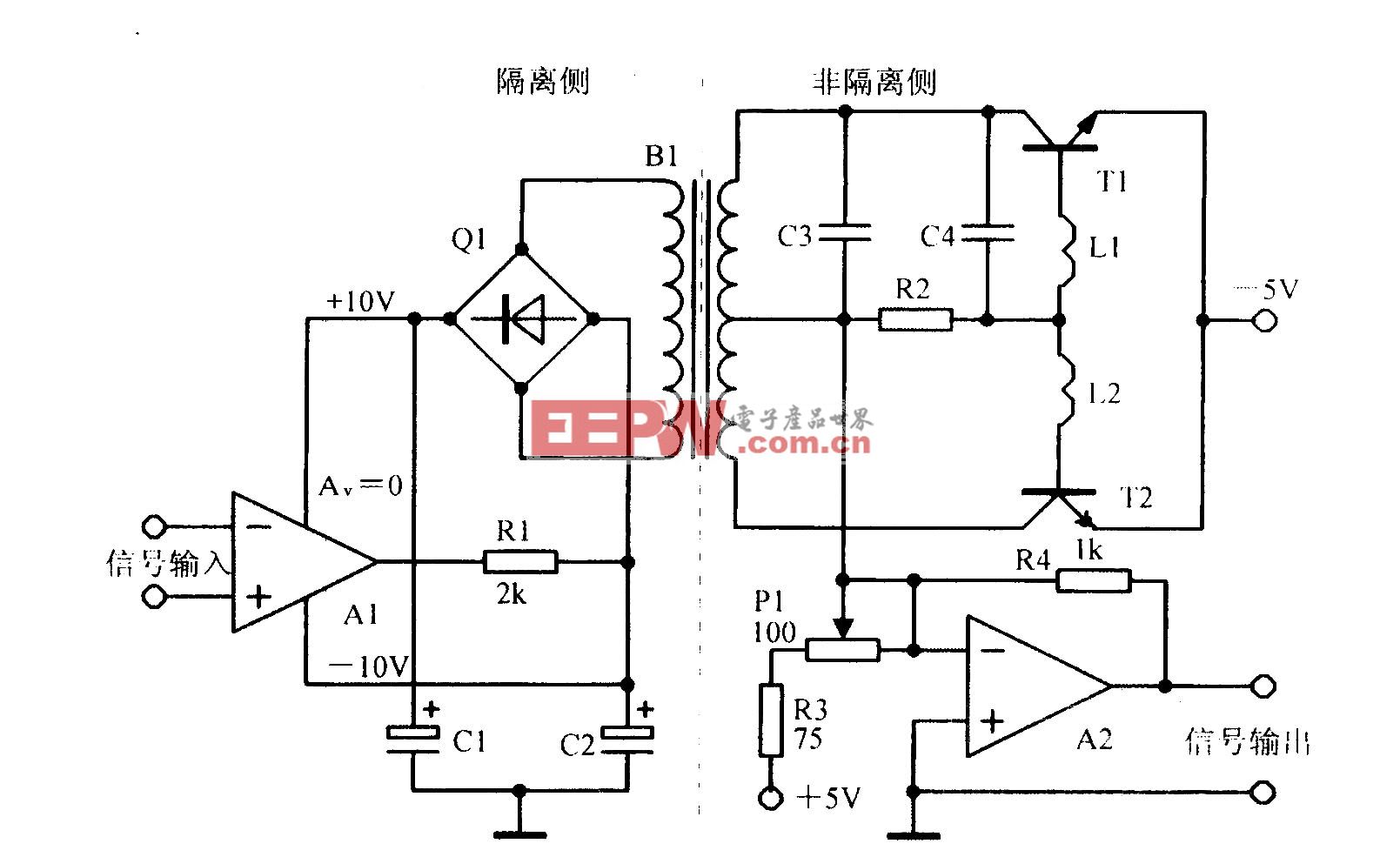

電壓基準(zhǔn)輸出電路由晶體管M14~M19,以及電阻R2,三極管Q1,電容C2組成。M18與M19鏡像PTAT電流同時(shí)M15與M17鏡像M18,M19支路的PTAT電流,組成電流放大,采用共源共柵結(jié)構(gòu)是為了鏡像更準(zhǔn)確。PTAT電流流過(guò)電阻R2,產(chǎn)生與溫度成正比的PTAT電壓,此PTAT電壓和二極管方式連接的三極管Q1的Vbe電壓疊加,產(chǎn)生與溫度無(wú)關(guān)的基準(zhǔn)電壓,電容C2是為了濾波,降低噪聲。

其中Eg為硅的帶隙能量;m為遷移率的溫度系數(shù)常數(shù)。

將式(7)代入(6)可以看出,只要合理設(shè)置晶體管的寬長(zhǎng)比和電阻R2,R1的比值就可以得到與溫度無(wú)關(guān)的基準(zhǔn)電壓。

由于電壓基準(zhǔn)源電路存在2個(gè)電路平衡點(diǎn),零點(diǎn)和正常工作點(diǎn)。當(dāng)基準(zhǔn)源工作在零點(diǎn)時(shí),晶體管M8,M9柵源電壓為高,M10,M11管柵源電壓為低,PTAT電路沒(méi)有電流產(chǎn)生,啟動(dòng)電路就是避免電壓基準(zhǔn)工作在零點(diǎn)上。本文提出的啟動(dòng)電路的最大特點(diǎn)是不耗電,它由晶體管M1~M5以及電容C1組成。當(dāng)電源電壓為低時(shí),若電容C1上存有電荷,則M3導(dǎo)通,將電荷放完,等電源電壓為高時(shí),M1,M2導(dǎo)通,流過(guò)M2的瞬間大電流迅速將M5打開(kāi),同時(shí)將M8,M9的柵電位拉低導(dǎo)通,產(chǎn)生PTAT電流,電路正常工作,當(dāng)M12,M13柵壓升高時(shí),M4導(dǎo)通,將M5柵壓拉低,啟動(dòng)電路停止工作,幾乎不消耗電流,達(dá)到了低功耗的目的。啟動(dòng)時(shí)間由M2管子的大小和電容C1決定。電壓基準(zhǔn)的啟動(dòng)電路仿真結(jié)果如圖3所示,啟動(dòng)時(shí)間只要50μs,啟動(dòng)之后只要消耗82 pA的電流。若沒(méi)有M3,電容C1上可能存在電荷沒(méi)有放完,再次啟動(dòng)時(shí)有啟動(dòng)不了的可能。

5 版圖及測(cè)試結(jié)果

本文介紹的電壓基準(zhǔn)源采用CSMC 0.5 μm,兩層POLY,一層金屬的CMOS工藝實(shí)現(xiàn),已經(jīng)成功流片。該工藝的閾值電壓分別為N管0.87 V,P管-0.97 V。由于產(chǎn)生PTAT電流的2個(gè)P型管存在失調(diào)會(huì)導(dǎo)致2支路不平衡,版圖匹配技術(shù)可以減少失調(diào),在版圖中可以增加虛擬晶體管使匹配晶體管間的環(huán)境相同來(lái)減少失調(diào),同時(shí),晶體管M7要在一個(gè)獨(dú)立的N阱中,使與M6的偏置條件一樣來(lái)減少失調(diào)。二極管可以用CMOS工藝中寄生的PNP三極管實(shí)現(xiàn),N阱中的P+區(qū)作為發(fā)射區(qū),N阱本身作為基區(qū),P型稱底作為集電區(qū),電阻采用具有負(fù)溫度系數(shù)的高阻POLY2電阻,方塊阻值為2 kΩ/□,節(jié)省面積。電壓基準(zhǔn)的版圖如圖4所示,版圖面積為:490μm×75μm-0.036 75 mm2。

基爾霍夫電流相關(guān)文章:基爾霍夫電流定律

評(píng)論