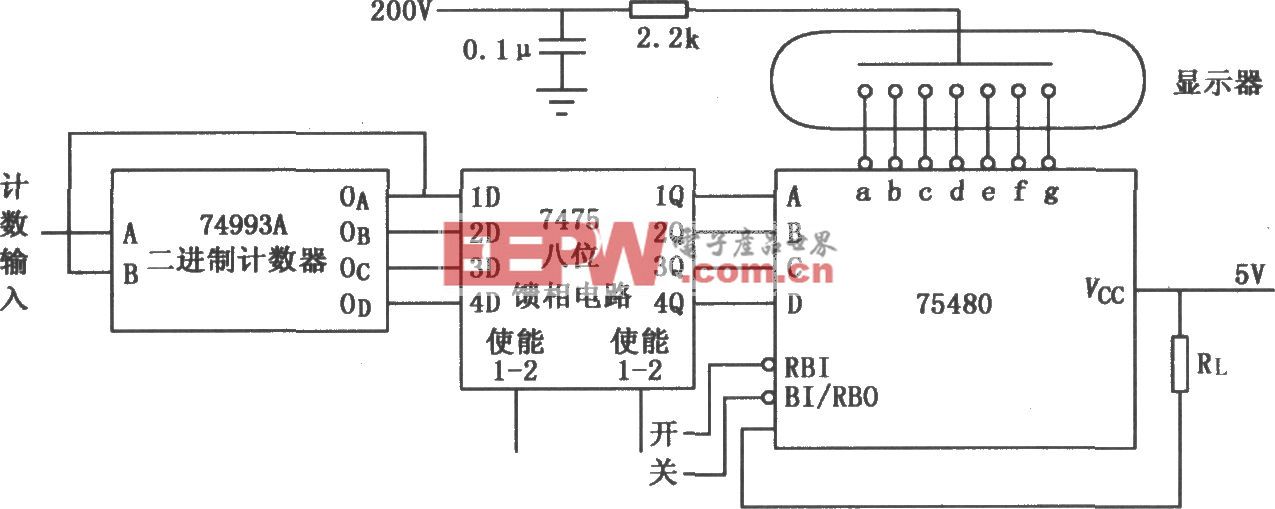

基于SOI高壓集成技術的電平位移電路設計

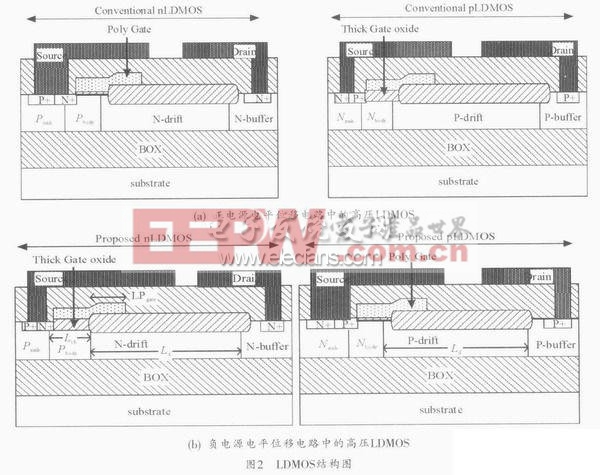

由于負電源供電的電平位移電路結構的改變,應用于正電源的常規nLDMOS和pLDMOS不能滿足該電路結構要求。在正電源供電的電平位移電路中,由于pLDMOS的源端接高壓電源,其柵源需要承受高壓,所以pLDMOS采用了厚柵氧的結構,如圖2(a)所示。在使用負電源的電平位移電路結構中(圖1(b)),pLDMOS的源端為邏輯高壓8V,柵端由低壓邏輯0~8V電壓控制,因此柵源不再承受高壓。但是nLDMOS的源端為負電源的最低電位,其柵源需要承受高壓,因此高壓nLDMOS需要采用厚柵氧結構,如圖2(b)所示。

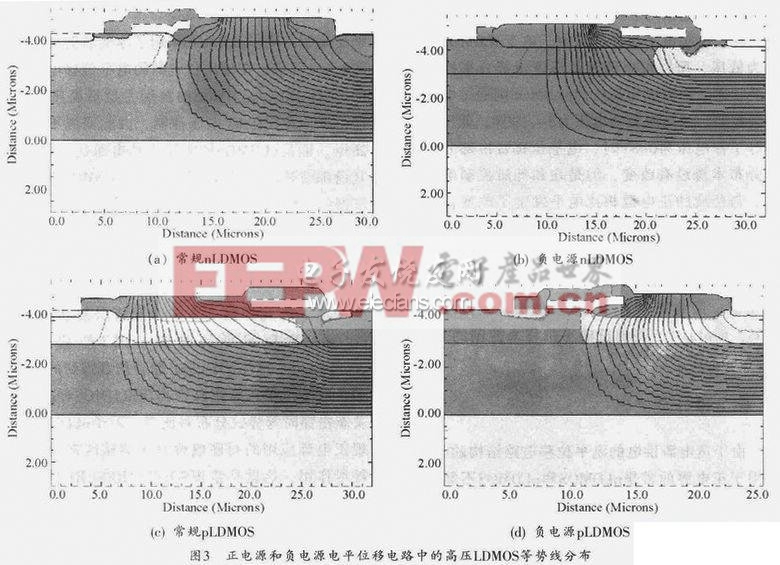

電源的改變不僅僅改變了電路的結構,nLDMOS的厚柵氧,同時器件的耐壓機理也發生了改變。考慮到低壓管的背柵效應,SOI材料的襯底只能接地,因此源漏電平的改變將引起nLDMOS和pLDMOS耐壓機理的改變。圖3是利用工藝(Tsuprem4)、器件(Medici)聯合仿真得到的正電源和負電源電平位移電路中高壓nLDMOS和pLDMOS關態擊穿時等勢線分布對比圖。對于nLDMOS,常規正電源應用的襯底電位對于漂移區來說是輔助耗盡作用,這就是常規SOI中的RESURF原理。但是對于負電源的nLDMOS來說,襯底不再起輔助耗盡SOI層漂移區的作用(圖3(b))。對于pLDMOS來說,情況剛好相反。所以針對負電源應用,兩種器件都要進行相應的優化處理。

利用工藝器件聯合仿真,在傳統的正電源應用的LDMOS基礎上對器件的結構參數進行優化設計。圖4(a)為pLDMOS在漂移區注入劑量Nd=7 e12cm-2時關態耐壓、開態耐壓與漂移區長度Ld(μm)的關系,以及在漂移區長度Ld=9μm情況下關態耐壓、開態耐壓與漂移區注入劑量Nd(cm-2)的關系。其他參數為:n型體區注入劑量5e12 cm-2,Nsink注入劑量3e15 cm-2,P-buffer注入劑量1.5e13 cm-2,溝道長度3μm,柵極場板3μm。從仿真結果可以看出:pLDMOS的關態耐壓隨漂移區的增加而增大,隨漂移區的注入劑量的增大先增大后減小;開態耐壓隨著漂移區注入劑量的增大而降低,但是在一定范圍內漂移區長度對其影響較小。總體上,pLDMOS的關態耐壓、開態耐壓都在160V以上,完全能夠滿足8~-100V工作電壓(108V耐壓)的要求。

圖4 (b)為nLDMOS在漂移區注入劑量Nd=4e11cm-2時關態耐壓、開態耐壓與漂移區長度Ld(μm)的關系,以及在漂移區長度Ld=15μm情況下關態耐壓、開態耐壓與漂移區注入劑量Nd(cm-2)的關系。其他參數為:p型體區注入劑量5e13 cm-2,Psink注入劑量3e15 cm-2,N-buffer注入劑量1e13cm-2,溝道長度3μm,柵極場板3.5μm。相對于pLDMOS,漂移區注入劑量和漂移區長度對于開態耐壓、關態耐壓的影響不大。同時關態耐壓都能維持在180V以上,但是開態耐壓卻只有90~120V,不能滿足8~100V工作電壓(108V耐壓)的要求。nLDMOS開態耐壓問題成為電路、器件設計的關鍵。

評論