電荷泵鎖相環(huán)的數(shù)字鎖定檢測電路應用分析

在數(shù)字鎖定檢測電路設計中,必須嚴格確保鎖定時的相位誤差Δt 小于鎖定檢測窗口TLock_Window,

否則數(shù)字鎖定指示信號就將出現(xiàn)誤判現(xiàn)象。根據(jù)前面分析得知,在CDCE72010 鎖相環(huán)電路中,外部

VCXO 的輸入阻抗是數(shù)字鎖定電路設計的一個關(guān)鍵參數(shù),根據(jù)式(2),可以得到壓控振蕩器輸入阻抗的指標要求:

![]()

假設在應用中CDCE72010 中鑒相頻率為1MHz,電荷泵電流為1,預設的鎖定檢測窗口為5.8ns,本

地VCXO 的壓控電壓為1.65V,則可以得到VCXO 的輸入阻抗要求:

![]()

在鎖相環(huán)電路設計中,鑒相頻率和電荷泵電流與環(huán)路直流增益成正比,跟鎖相環(huán)的環(huán)路帶寬和相位裕量密切相關(guān),為了得到較小的環(huán)路帶寬,通常需要降低鑒相頻率或電荷泵電流。進一步分析式(2),相位誤差跟鑒相頻率和電荷泵電流成反比,因此在低環(huán)路帶寬電路的設計中,必須特別注意壓控振蕩器的輸入阻抗(或漏電流指標)和鎖定檢測窗口的設計,嚴格滿足式(3)的設計要求。

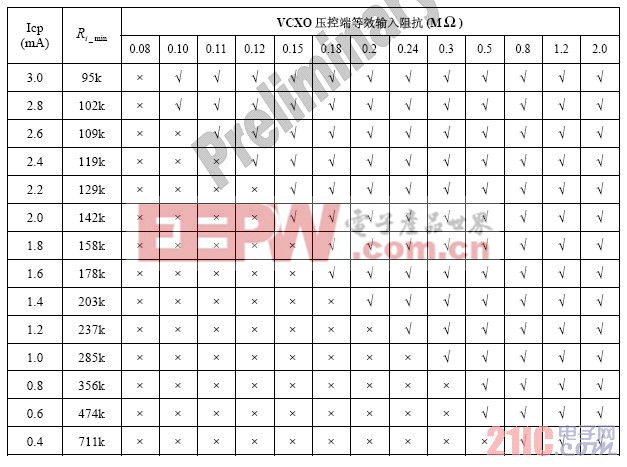

可以通過實驗來檢查式(3)的正確性。在CDCE72010 的評估板上,改變VCXO 壓控端的等效輸入阻抗,通過觀察CDCE72010 鎖定指示輸出管腳或鎖定指示寄存器的鎖定狀態(tài),分析該鎖定檢測電路是否可靠地工作,具體實驗設置如下:

參考時鐘為25MHz,VCXO 頻率為125MHz,鑒相頻率為1MHz,PFD 的檢測窗口為5.8ns,控制電

壓為1.65V,實驗結(jié)果如表1 所示,其中R i _ min為計算出的VCXO 輸入阻抗的最小值,√表示鎖相環(huán)指示鎖定,×表示鎖相環(huán)數(shù)字鎖定指示為失鎖狀態(tài)。其中,在實驗過程中,由示波器監(jiān)控CDCE72010 的參考時鐘和本振時鐘一直處于鎖定狀態(tài)。

表1 不同VCXO 輸入阻抗值對CDCE72010 數(shù)字鎖定指示的影響

從表1 中可以看出VCXO 的輸入阻抗對鎖相環(huán)的數(shù)字鎖定有很大的影響,例如當電荷泵電流為1.2mA 時,根據(jù)式(3)可以得到VCXO 的最小輸入阻抗為237Kohms,那么對于低于這個值的輸入阻抗,數(shù)字鎖相指示無法正確指示鎖定,實驗測試的結(jié)果與理論分析是吻合的。

4 總結(jié)

本文在電荷泵鎖相環(huán)數(shù)字鎖定檢測工作原理的基礎(chǔ)上,分析了影響鎖定時相位誤差的環(huán)路參數(shù)和外圍元器件的關(guān)鍵參數(shù),包括電荷泵電流、鑒相頻率和漏電流等。同時根據(jù)對整個環(huán)路漏電流路徑的分析,重點分析了外部壓控振蕩器的等效輸入阻抗對鎖相環(huán)鎖定指示準確性的影響。

以CDCE72010 數(shù)字鎖定設計為例,為了提高數(shù)字鎖定檢測電路鎖定狀態(tài)指示的準確性,在低環(huán)路帶寬的鎖相環(huán)電路設計中,必須選擇恰當?shù)耐獠繅嚎卣袷幤鞯妮斎胱杩箙?shù)指標。

DIY機械鍵盤相關(guān)社區(qū):機械鍵盤DIY

低通濾波器相關(guān)文章:低通濾波器原理

電荷放大器相關(guān)文章:電荷放大器原理 電流傳感器相關(guān)文章:電流傳感器原理 鑒相器相關(guān)文章:鑒相器原理 數(shù)字濾波器相關(guān)文章:數(shù)字濾波器原理 鎖相環(huán)相關(guān)文章:鎖相環(huán)原理 鎖相放大器相關(guān)文章:鎖相放大器原理

評論