一種高效率AC/DC電源的設(shè)計

導(dǎo)通損耗

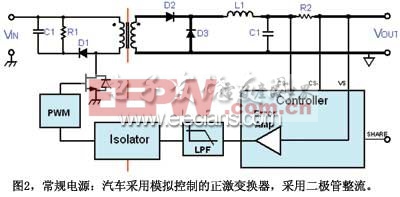

常規(guī)的技術(shù)采用二極管來進(jìn)行整流。二極管與主功率通道(見圖2的D2)相串聯(lián)。它一般需要產(chǎn)生0.7V的電壓降才能開啟導(dǎo)通。在一個3.3VOUT的系統(tǒng)中,這意味著二極管將耗散大約(0.7V/3.3V) = 21%的輸出功率,這意味著效率上的極大損失。在一個12VOUT的電源中,二極管將造成約6%(0.7V / 12V)的效率損失。其影響隨著輸出電壓的上升而降低。正因?yàn)槿绱耍覀兂3?梢栽谳敵鲭妷焊叩碾娦艖?yīng)用(48V)中看到二極管整流的應(yīng)用。

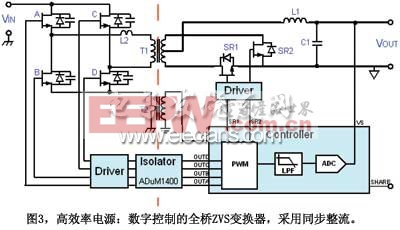

使用同步整流能極大地提升效率。同步整流一般采用一個MOSFET開關(guān)而不是二極管(見圖3中的SR1和 SR2)。在關(guān)斷時,MOSFET可以阻止負(fù)向電壓,僅傳導(dǎo)正向電流,它不需要出現(xiàn)正向壓降即可實(shí)現(xiàn)導(dǎo)通。相反,開關(guān)電流造成的損耗由MOSFET的RDS(ON)來決定。RDS(ON)的典型值約為5mΩ。不過,在一個100A的電源中,這會帶來5mΩ × 100A= 500mV的電壓降,幾乎與一個二極管相當(dāng)。因此,大電流的電源需要將多個MOSFET并聯(lián)起來,以減少等效的RDS(ON),從而進(jìn)一步降低導(dǎo)通損耗。這是具有低輸出電壓、大輸出電流的電源所采用的標(biāo)準(zhǔn)設(shè)計方法,也應(yīng)用于高效率電源設(shè)計中。對同步整流開關(guān)的時序關(guān)系的優(yōu)化也很關(guān)鍵,否則,就體現(xiàn)不出來同步整流的優(yōu)點(diǎn)。

開關(guān)損耗

在減小開關(guān)電源的尺寸和重量方面所遇到的主要障礙是開關(guān)頻率。開關(guān)頻率與效率直接相關(guān)。技術(shù)的發(fā)展趨勢是提高開關(guān)頻率,但是,隨著開關(guān)頻率的增加,開關(guān)的損耗也會上升。開關(guān)的損耗是由于開關(guān)的非理想因素所造成的(雜散電容和非零的開關(guān)時間)。因此,必須實(shí)現(xiàn)某種折中平衡。正是基于這些原因,大多數(shù)可買到的隔離型開關(guān)電源的開關(guān)頻率在50kHz~400kHz之間。

在功率晶體管中出現(xiàn)的開關(guān)損耗包括導(dǎo)通損耗和關(guān)斷損耗兩部分。導(dǎo)通損耗由流過晶體管的寄生電容和電源變壓器的初級繞組的電流所造成。關(guān)斷損耗由晶體管的關(guān)斷動態(tài)過程所決定。由于開關(guān)兩端的電壓可以遠(yuǎn)大于100V,這會造成相當(dāng)大的損耗。既然開關(guān)損耗的高低直接取決于開關(guān)時的電流和電壓差,很顯然,在開關(guān)時保證電流或者電壓為零,就可以消除這些損耗。這是MOSFET成為廣泛使用的功率晶體管的原因之一。它們的電流下降時間很短,因此MOSFET兩端的電壓顯著增加之前,電流就幾乎下降到零。

零電壓開關(guān) (ZVS)可用于改善效率。ZVS控制開關(guān)的時序關(guān)系,使之在電感電流接近零時關(guān)斷。當(dāng)MOSFET開關(guān)的時序被控制為與輸入波形的過零點(diǎn)同步時,開關(guān)損耗將得以降低。ZVS的一個實(shí)現(xiàn)方式(見圖3),即添加電感L2。這也是ZVS成為隔離型電源中的常用方法的一個原因。它可以實(shí)現(xiàn)在變壓器尺寸和開關(guān)損耗方面實(shí)現(xiàn)良好的平衡。數(shù)字控制器提供了能夠充分利用ZVS的能力,因?yàn)樗鼈儽饶M控制器對波動的補(bǔ)償要容易得多。

磁損

變壓器磁芯的損耗由兩個因素造成:磁滯和渦流損耗。磁滯損耗是磁化的交流電流的上升、下降以及方向的改變使得磁場方向不斷顛倒所致。渦流損耗是感應(yīng)出的電流在磁芯中循環(huán)流動的結(jié)果。負(fù)載損耗則隨著變壓器的負(fù)載變化而變化。它們包括了變壓器的初級和次級線圈導(dǎo)體的熱損耗和渦流損耗。繞組材料中的熱損耗(也稱為I2R損耗)是負(fù)載損耗中的最大的一部分,由變壓器中導(dǎo)體的寄生電阻產(chǎn)生。通過采用每單位截面積的電阻很小的材料,可以減小這一電阻,但不會顯著增加變壓器的成本。

dc相關(guān)文章:dc是什么

評論