高頻率、高輸入DC/DC轉換器設計實例

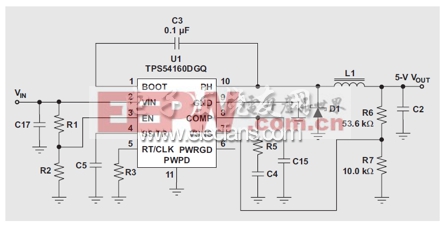

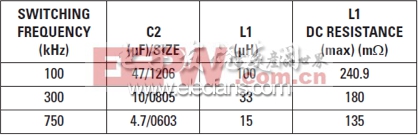

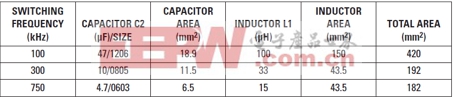

圖1所示電路用于評估實驗臺上每種設計的性能。示意圖中沒有值的一些組件,為設計中修改了的組件。輸出濾波器由L1和C2組成。所有三種設計的組件值都列舉在表1中,這些值的選擇是基于方程式1a到2b的結果。注意,每個電感的DC電阻隨頻率增加而減小。這是因為較少的匝數所需的銅長度更短。我們單獨為每個開關頻率設計了誤差放大器補償組件。選擇補償值的計算方法,超出了本文討論的范圍。

最小“導通”時間

最小可控“導通”時間限制是DC/DC轉換器IC的一個特點,其為脈寬調制(PWM)電路的最窄可達脈寬。在降壓轉換器中,開關周期期間功率MOSFET導通的時間百分比被稱作占空比,其等于輸出電壓與輸入電壓的比。使用TPS54160轉換器時,占空比為0.104(4 V/48 V),而數據表中列出的最小“導通”時間為130 ns。可控脈寬限制產生一個最小可達占空比,而用最小“導通”時間乘以開關頻率,我們可以輕松地計算出該占空比的大小。一旦知道了最小占空比,利用VIN乘以最小占空比,我們便可以計算出最低可達輸出電壓。最低輸出電壓同樣也受轉換器基準電壓的限制,使用TPS54160時其為0.8V。

本例中,我們可以通過750-kHz開關頻率來產生一個5-V輸出電壓(參見表2)。但是,如果該頻率為1 MHz,則最低可能輸出電壓被限制為約6V;否則,DC/DC轉換器會跳過脈沖。替代方法是降低輸入電壓或者頻率。在選擇某個開關頻率以前,你最好是先查看DC/DC轉換器數據表,了解保證最小可控“導通”時間。

脈沖跳躍

DC/DC轉換器無法足夠快速地清除門驅動脈沖來維持理想占空比時,便會出現脈沖跳躍。電源會嘗試調節輸出電壓,但由于距離更遠的脈沖,紋波電壓會增加。由于存在脈沖跳躍,輸出紋波會呈現出分諧波成分,其可能出現噪聲問題。限流電路也可能不再正常工作,因為IC可能不響應大電流峰值。一些情況下,如果控制器不正常工作,控制環路便可能會不穩定。

效率和功耗

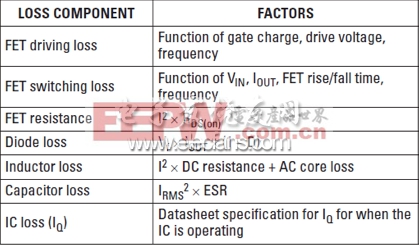

DC/DC轉換器的效率,是進行電源設計時需要考慮的最重要屬性之一。低效率會轉換成高功耗,必須要在印刷電路板(PCB)上使用單獨的散熱器或者更多的銅,才能處理這些功耗。功耗也對電源上游器件提出了更高的要求。如表3所示,功耗共有幾個組成部分。

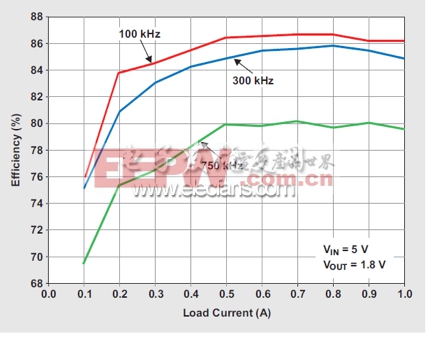

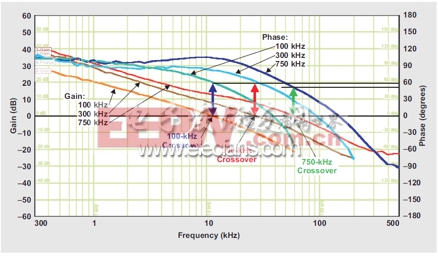

三個例子的重要損耗組成部分,來自于FET驅動損耗、FET開關損耗和電感損耗。FET電阻和IC損耗是一致的,因為所有三個設計中都使用了相同的IC。由于所有例子中都選擇了低ESR的陶瓷電容,因此電容損耗可以忽略不計。為了表明高頻開關的影響,我們對每個例子的效率都進行了測量,并將其顯示在圖2中。該圖清楚地表明,效率隨開關頻率增加而下降。若想提高所有頻率下的效率,需要尋找到一種全負載狀態下低漏到源“導通”電阻、低門電荷或者低靜態電流規范的DC/DC轉換器;或者尋找到一些具有更低等效電阻的電容和電感。

表 1 三個舉例電源設計的電容和電感選擇

表 2 130-ns最小“導通”時間的最小輸出電壓

表 3 功耗組成部分

圖 2 三個舉例頻率下 TPS54160 的效率

組件尺寸

表4列出了三種設計要求的總電路板面積,以及電容和電感的焊盤面積。電容或者電感的建議焊盤面積,稍稍大于單個組件本身,且三種設計舉例均使用了該面積。每個組件占用的面積相加(其包括IC、濾波器以及所有其它小型電阻器和電容的焊盤尺寸),然后將得到的結果乘以2倍(考慮到組件的間距),便得到總面積。100-kHz和750-kHz設計之間存在近250 mm2的總面積節省,從而使濾波器體積縮小50%,而板空間占用減少55%。但是,存在收益遞減規律,因為電容和電感值無法減少至零!換句話說,不斷推高頻率并不能夠一直減小總尺寸,因為你無法總是能夠在市場上買到這些尺寸適合且批量生產的電感和電容。注意,33-µH和15-µH電感占用相同的面積。存在這種可能性,是因為33-µH電感的高度為3.5 mm,而15-µH電感僅高2.4 mm。我們想通過這兩種電感來說明的觀點是:電感與體積成正比例關系。

表 4 組件尺寸和總面積要求

圖 3 100kHz、300 kHz和750 kHz 的波特圖

評論