大功率VDMOS(200 V)的設(shè)計(jì)研究

1.6 結(jié)終端仿真結(jié)果

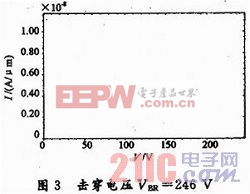

結(jié)終端結(jié)合自對(duì)準(zhǔn)工藝,P等位和場(chǎng)限環(huán)的形成依靠多晶和場(chǎng)氧進(jìn)行阻擋,利用多晶硅作為金屬場(chǎng)板。使用了1個(gè)等位環(huán)和3個(gè)場(chǎng)限環(huán),耐壓可以達(dá)到242 V,仿真結(jié)果如圖3~5所示。本文引用地址:http://www.104case.com/article/178213.htm

2 制造結(jié)果

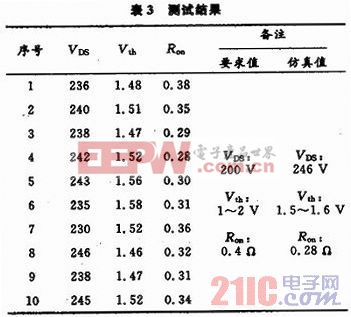

在基于設(shè)計(jì)和封裝控制的基礎(chǔ)上,進(jìn)行了樣品的試制。采用的是TO-257的扁平封裝。管芯試制樣品后,對(duì)相關(guān)參數(shù)進(jìn)行了測(cè)試,測(cè)試結(jié)果見表3所示。因?yàn)閷?dǎo)通電阻是在封裝之后測(cè)試,在封裝后會(huì)引入一定的封裝電阻,所以導(dǎo)通電阻比仿真時(shí)略有增大。隨后對(duì)管芯進(jìn)行了封裝,試驗(yàn)產(chǎn)品出來后,發(fā)現(xiàn)有近一半產(chǎn)品的閾值電壓有所縮小,有的甚至降到1V以下。出現(xiàn)這一問題,及時(shí)查找原因,發(fā)現(xiàn)燒結(jié)時(shí)間過長可能是閾值電壓縮小的主要原因。由于本產(chǎn)品外形的特殊性,燒結(jié)時(shí),每一船放的產(chǎn)品只數(shù)不能過多。而量少了,原來的燒結(jié)時(shí)間就顯得過長。燒結(jié)時(shí)使用的是氫氣保護(hù),燒結(jié)時(shí)間長了,使氫離子在柵極上堆積,致使閾值電壓下降。于是嘗試著將燒結(jié)時(shí)間縮短,可是燒出來又出現(xiàn)了新的問題:很多產(chǎn)品的燒結(jié)焊料熔化不均勻,使芯片與底座燒結(jié)不牢,用探針一戳,就掉下來了。為了解決這一矛盾,反復(fù)試驗(yàn)將燒結(jié)時(shí)間用秒數(shù)來增減。最終達(dá)到在焊料完全均勻熔化的前提下,又使閾值電壓不至于縮小。

3 結(jié)語

200V VDMOS器件的設(shè)計(jì)主要受到擊穿電壓和導(dǎo)通電阻兩個(gè)參數(shù)的相互影響和相互制約,在設(shè)計(jì)中應(yīng)優(yōu)化兩個(gè)參數(shù)的范圈。在滿足其中一個(gè)的條件下使另一個(gè)達(dá)到最優(yōu)的選擇,采用仿真設(shè)計(jì)可大大減少設(shè)計(jì)成本。

評(píng)論