14位Pipeline ADC設(shè)計(jì)的帶隙電壓基準(zhǔn)源技術(shù)介紹

2.2基準(zhǔn)輸出與溫度的關(guān)系

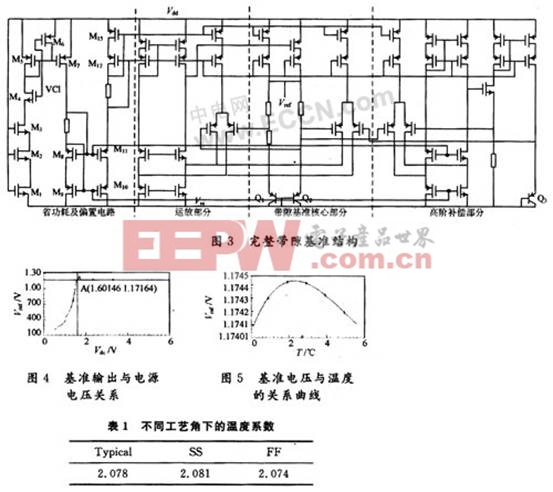

圖5是典型工藝角下經(jīng)過(guò)高階曲率補(bǔ)償?shù)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/基準(zhǔn)">基準(zhǔn)電壓與溫度的關(guān)系曲線。由圖計(jì)算得到在典型(TT)工藝角下,電源電壓為3.3 V時(shí),在-40~+100℃工作溫度范圍內(nèi),該基準(zhǔn)電壓溫度系數(shù)為2.077 ppm/℃。在整個(gè)工作溫度范圍內(nèi),基準(zhǔn)輸出電壓隨溫度變化不超過(guò)±0.15%。另外,由同種工作條件和模擬條件得到該基準(zhǔn)在其他兩個(gè)工藝角溫度系數(shù)如表1所示。可見(jiàn),該電路具有很好的溫度特性。

2.3 與參考文獻(xiàn)性能比較

與參考文獻(xiàn)性能比較如表2所示。

表2為本文設(shè)計(jì)電路與文獻(xiàn)[6]和文獻(xiàn)[7]中電路的模擬仿真結(jié)果比較。本文電路的供電電壓可以低至1.6 V,輸出電壓1.174 V.在-40~100℃時(shí)溫漂約為2ppm/℃,且功耗最高不超過(guò)110 μW。由此可見(jiàn),本文設(shè)計(jì)電路具有低電壓低功耗和低溫漂的優(yōu)點(diǎn),綜合性能優(yōu)異。

3 版圖設(shè)計(jì)

模擬電路的版圖設(shè)計(jì)中器件的匹配以及合理的布局布線對(duì)電路性能的影響很大。再考慮到要減小工藝失配的影響,需要對(duì)版圖進(jìn)行精心設(shè)計(jì)。版圖設(shè)計(jì)注意以下幾點(diǎn):

(1)運(yùn)放的輸入管采用大的寬長(zhǎng)比例,以減小運(yùn)放的失調(diào)電壓,并且其晶體管的溝道要大于工藝最小溝長(zhǎng)Lmin。

(2)電路中的關(guān)鍵器件PNP Bipolar晶體管,在實(shí)際電路設(shè)計(jì)中取Q1與Q2的面積比為8:1,然后采用中心對(duì)稱的設(shè)計(jì)方法,實(shí)現(xiàn)器件的匹配。

(3)集成電路中電阻誤差很大,采用電阻分級(jí)并聯(lián)方式,并在電阻周圍加上dummy電阻,以減少環(huán)境的影響,增強(qiáng)電阻匹配性。

4 結(jié) 語(yǔ)

與其他許多高階曲率補(bǔ)償帶隙電路相比,本文提出的這種帶隙基準(zhǔn)電壓源,具有低電壓低功耗和低溫漂的優(yōu)點(diǎn),且與標(biāo)準(zhǔn)CMOS工藝兼容,結(jié)構(gòu)新穎,綜合性能優(yōu)異,完全符合設(shè)計(jì)要求。可以很好地應(yīng)用于高精度比較器、A/D和D/A轉(zhuǎn)換器等模擬集成電路中,該電壓源采用0.35μm CMOS工藝,Spectre仿真表明,在-40~100℃時(shí),其溫度系數(shù)為2 ppm。這種帶隙基準(zhǔn)可用于14位pipeline ADC中,應(yīng)用前景廣泛。本文引用地址:http://www.104case.com/article/177913.htm

評(píng)論