基于集成計數器的N進制計數器設計與仿真

2.3 基于74LS161的三十六進制加法計數器的設計與仿真(以十進制數方式顯示)

計數狀態以十進制數方式顯示,讀數方便,符合多數人的習慣。若無十進制計數器74LS160,用十六進制計數器74LS161也可構成以十進制數方式顯示的三十六進制加法計數器,但設計較為復雜。以下介紹一種設計方法。

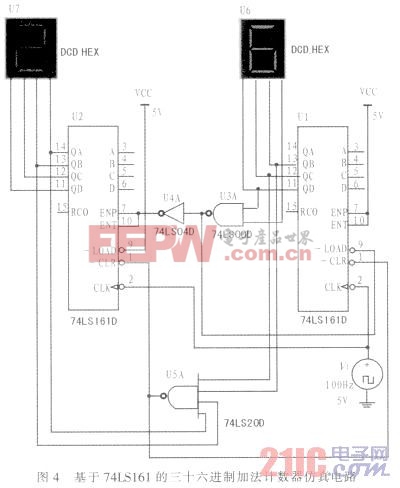

1)確定級聯邏輯:共需要2個74LS161,設低位的74LS161編號為1,高位的74LS161編號為2,采用與圖2和圖3同樣的同步級聯方式,即外接脈沖同時接入高、低位2個74LS161的計數脈沖輸入端CLK。低位74LS161的計數控制端ENP和ENT都接高電平,即ENP1=ENT1=1,使其工作于計數狀態。因為要采用十進制數方式顯示,則低位74LS161最大輸出狀態1SN-1=1S9=Q1DQ1CQ1BQ1A=1001,此時其進位輸出RCO1=0,不能用于控制高位74LS161進行計數。高位74LS161的計數控制端ENP和ENT可由低位最大狀態的非完成譯碼控制,即ENP2=ENT2=Q1DQ1A。設初態為全零狀態,每來一個時鐘,低位74LS161記一次數,狀態代碼加1,第9個時鐘到來后,高位74LS161計數控制端有效,第10個時鐘到來,低位74LS161清零的同時,高位74LS161記一次數。

2)低位74LS161的歸零邏輯:用同步置數控制端

3)整體歸零邏輯:設計三十六進制計數器,設初始計數狀態顯示為00,則最大狀態顯示為35,可用兩個74LS161的異步清零控制端完成整體清零。整體最大狀態SN=S36=(00110110)8421BCD,

4)在仿真平臺Multisim中選擇2個74LS161,74LS00、74LS04、74LS20各1個,2個5 V電源和地,根據歸零邏輯創建仿真電路;

5)時鐘電壓源V1接入計數脈沖輸入端CLK,用帶譯碼的十六進制數碼管U6和U7作狀態輸出的顯示器,完整的三十六進制計數器仿真電路如圖4所示。本文引用地址:http://www.104case.com/article/177465.htm

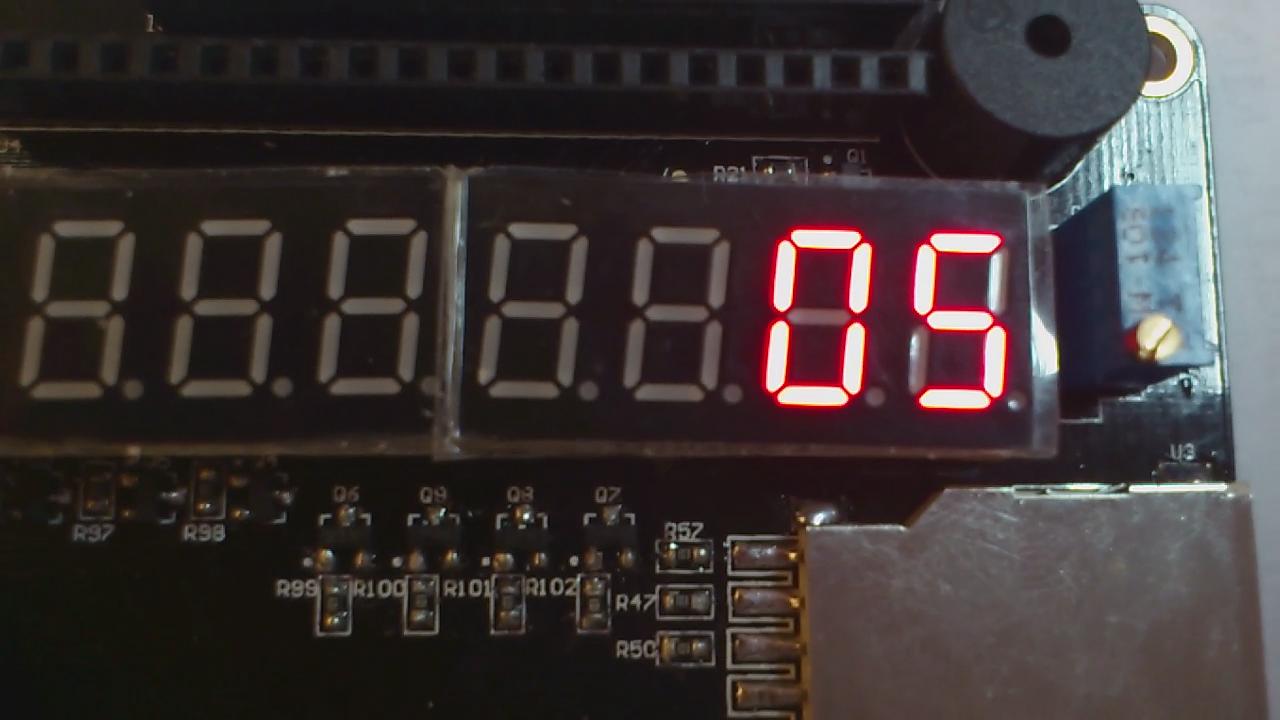

運行仿真電路,在時鐘控制下,數碼管U7和U6以2位十進制數方式循環顯示00,01,02,…35,00,…,共36種輸出狀態,顯示結果與圖3電路顯示相同。因此,圖4電路用74LS161實現了以十進制數方式顯示的三十六進制加法計數功能。

3 結束語

計數器具有計數、分頻、定時等功能特點,廣泛應用于數字測量、控制等數字系統,掌握N進制計數器的設計方法有著理論和實踐意義。文中以集成計數器74LS161和74LS160為基礎,采用歸零法,多方式地實例設計了36進制計數器,設計原理清晰,邏輯嚴謹;電路簡單,易于實現。應用Multisim 10進行電子電路設計和仿真,可用大量豐富的元器件庫和實用的虛擬儀器,操作簡單,搭建電路方便、快捷,并且修改電路方便.是現代電子設計的有效方法。基于集成計數器的N進制計數器設計方法有推廣價值,用非十進制集成計數器設計以十進制數方式顯示的N進制計數器有創新性。

評論