基于集成計數器的N進制計數器設計與仿真

運行仿真電路,在時鐘控制下,數碼管U5和U4以2位十六進制數方式循環顯示00,01,02,…,09,0A,0B,…,0F,10,11,…,23,00,…,共36種輸出狀態,本質上是8個計數輸出端Q2D~Q2AQ1D~Q1A對應二進制代碼以00000000,00000001,…,00100011,00000000,…。循環變化,共36種輸出狀態。因此,圖2電路用74LS161實現了三十六進制加法計數功能。

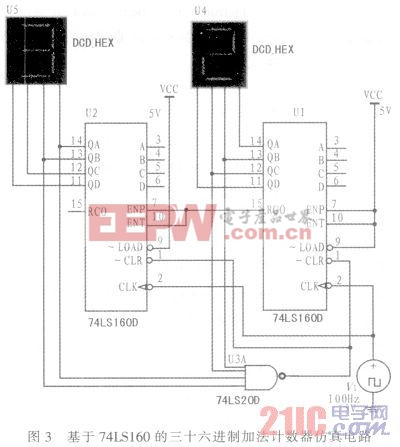

2.2 基于74LS160的三十六進制加法計數器的設計與仿真

74LS160為十進制計數器,其計數狀態QDQCQBQA以8421BCD碼的方式輸出,最大狀態為1001。設計三十六進制計數器需要2個74LS160通過級聯的方法,可先擴展成100(10x10)進制計數器。設低位的74LS160編號為1,高位的74LS160編號為2,再用歸零法設計如下:

1)寫出SN的8421BCD碼:SN=S36=(00110110)8421BCD;

2)求出歸零邏輯:

3)在仿真平臺Multisim中選擇2個74LS161,1個74LS20,2個5 V電源和地,根據歸零邏輯創建仿真電路;

4)時鐘電壓源V1接入計數脈沖輸入端CLK,用帶譯碼的十六進制數碼管U4和U5作狀態輸出的顯示器,完整的三十六進制計數器仿真電路如圖3所示。本文引用地址:http://www.104case.com/article/177465.htm

運行仿真電路,在時鐘控制下,數碼管U5和U4以2位十進制數方式循環顯示00,01,02,…35,00,…,共36種輸出狀態,本質上是8個計數輸出端Q2D~Q2AQ1D~Q1A對應8421BCD碼以初態00000000,隨著時鐘的到來依次加1,直到00110101,00000000,…,循環變化,共36種輸出狀態。因此,圖3電路用74LS160實現了三十六進制加法計數功能。

評論