KAI-02150的CCD模擬前端采集電路設計

2.2 時序控制采集電路的設計

傳統CCD時序控制采集電路主要由CPLD和相關雙采樣A/D芯片組成,垂直時鐘由CPLD提供,而水平時鐘和電荷復位時鐘則由A/D芯片提供。為滿足多種工作模式的切換,必須預存多種驅動時鐘的輸出樣式,這樣需要在CPLD中編寫多種垂直時鐘時序樣式,大大增加了代碼開發的工作量。此外傳統方案外圍電路復雜,驅動時鐘信號源需要CPLD和A/D同時提供,在集成度、靈活性和穩定性上都有所欠缺。

文中采用兩片Analog Device公司生產的AD9920A來進行精確的CCD時鐘信號時序的輸出和對CCD信號的進行A/D轉換。AD9920A主要特點如下:12位40.5 MHz模數轉換器;內置相關雙采樣控制電路;集成精確時序控制器;支持24路可編程垂直時鐘信號輸出。由于所有驅動時鐘和復位信號均由AD9920A提供,與傳統方案相比,文中采用的方案可以通過SPI接口配置AD9920A自身寄存器,預存多種時鐘驅動樣式,更加靈活方便地進行配置出多種攝像機工作模式,并且具有更高的穩定可靠性。

方案中所采用的兩片AD9920A中一片工作在Master模式,用來提供CCD所需的水平垂直時鐘、電荷復位信號和電子快門信號,并對通道A的CCD信號進行采集。另外一片工作在Slave模式,對通道B進行信號采集。工作在Master模式的AD9920A產生的HD和VD同步信號輸入到Slave模式的AD9920A,以便同步CCD數字信號輸出,在FPGA中雙通道采集的圖像可以得到還原。

2.3 時鐘驅動電路的設計

KAI-02150的時鐘驅動信號高低電平要求各不相同,前級AD9920A所提供的TTL時鐘信號必須通過時鐘驅動電路來進行電壓轉換,以符合CCD驅動電平的要求。

時鐘驅動電路主要作用是為時鐘信號提供直流偏置與增大時鐘驅動能力。文中采用DC12V電壓供電,由雙通道DC/DC轉換器LT3471得到16 V和-10 V電壓,后經LDO穩壓芯片LT1964和LT1761得到CCD垂直時鐘所需的-9 V和12 V直流偏置電壓。而水平時鐘信號、復位信號和電子快門的直流偏置電壓則主要由兩片雙極性D/A轉換器AD5734R產生,后經LT1010電源緩沖器來提高電流輸出能力。

前級Master模式的AD9920A輸出的水平時鐘信號與復位信號經74LCX541 8路三態CMOS緩沖器輸入。為避免信號產生過多失真,在PCB布線時HL、H1、H2和RG走線的電感應非常低。為使互感最小,互補信號H1和H2的布線應盡可能對稱并靠近。H5和H6信號也應如此。CCD對HL和H1至H6有很大的瞬變電流要求,因此使用較寬的PCB走線。

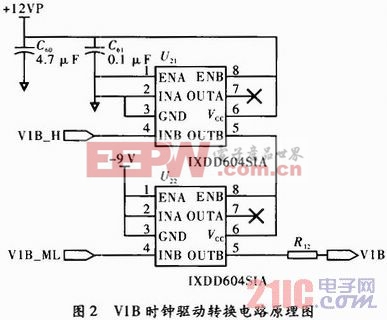

垂直時鐘信號經IXDD604高速MOSFET驅動器輸入到CCD,垂直時鐘信號VIB有高中低3個電平狀態。文中使用AD9920A輸出的兩個垂直時鐘信號經過兩片IXDD604來產生所需要的V1B時鐘。如圖2所示,當V1B_H為低時,U22的VCC為0 V,V1B可以根據V1B_ML輸出中低電平。當V1B_H為高時,U22的VCC為12 V,保持V1B_ML為高使得V1B輸出12V。本文引用地址:http://www.104case.com/article/177383.htm

電子快門信號的直流偏置電壓由AD5734R和LT1761提供,VSUB信號由AD9920A的GPO經過三極管推挽放大電路后產生。

評論