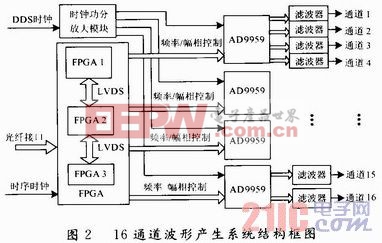

應用于數字陣列的多通道波形產生系統設計

2.2 多通道波形產生系統軟件設計

在數字陣列雷達中,波束控制系統根據雷達整機發射信號的要求,計算低副瓣幅度加權、波束掃描相位加權以及幅相誤差校正所需的幅相加權因子,確定每個發射通道波形的控制碼,波形產生系統通過接口電路獲得波形控制碼,在FPGA中完成對波形控制碼的譯碼,確定頻率、幅相控制字,控制AD9959每個通道的波形樣式。AD9959的相位累加器為32位,調頻數據累加器為32位,相位偏移累加器為14位,幅度系數乘法器為10位。計算公式如下:

式中:FTW為頻率控制字;fs為系統時鐘率;POW為相位偏移字;AW為幅度調節字。

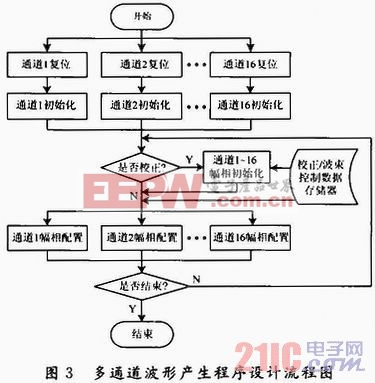

對AD9959的內部寄存器的配置是通過串口實現的。其中管腳SCLK是串行時鐘腳,用于同步AD9959的數據。CS管腳是片選腳,只有CS腳處于低電平時,芯片才進入通信周期。SD1O管腳是串行數據腳。串口操作有三種操作模式:單比特串行模式、2比特串行模式和4比特串行模式。其中單比特模式只需要一根數據線,可以盡量減小線間信號串擾,因此設計中采用該模式完成對AD9959的讀寫操作。對AD9959的控制流程如下:在主復位信號后,提供通道使能位與頻率調節字FTW的地址(Reglster 0x04)和相位偏移調節字POW的地址(Register 0x05)相結合,這樣,頻率調節字和/或相位偏移字就可在四個通道間獨立編程。圖3給出了程序設計流程圖。

2.3 系統電磁兼容設計

本設計中,系統中包含4片AD9959芯片、3片高速FPGA以及多片時鐘驅動電路、變壓器、濾波器電路,是一個復雜的數/模混合電路系統,尤其是要在單塊PCB板上完成了16路波形通道的系統集成,電磁兼容設計是必須充分考慮的問題。在電路設計中選取合適的電路結構,注意各功能模塊之間的阻抗匹配、電平匹配;在PCB設計中,首先根據電源電壓高低、數字器件或模擬器件、高速器件或低速器件以及電流大小等特點,將電路劃成不同的功能組:電源部分、接口部分、數字部分(包括AD9959數字控制入口、FPGA及附屬電路)、模擬部分(包括AD9959模擬輸出、時鐘驅動、匹配電路、濾波電路等),然后根據PCB的尺寸、安裝要求對電路的全部元件進行綜合的合理布局。每個功能組的元器件緊湊地放置在一起以得到最短信號路徑以減小反射,尤其是時鐘線和AD9959輸出信號線應盡量短,設計中采取差分傳輸的方式。其次,須仔細考慮多層PCB板的層設置,根據電源、地的種類、信號線的密集程度、信號頻率等確定合適的PCB板層,層排列則依據一些基本原則:關鍵電源平面與其對應的地平面相鄰;相鄰層的關鍵信號不能跨分割區;時鐘等關鍵信號有一相鄰地平面等。

評論