應用于數字陣列的多通道波形產生系統設計

摘要:直接數字頻率合成(DDS)是數字陣列雷達(DAR)實現收發數字波束形成的關鍵技術之一。給出了一種基于DDS技術的多通道波形產生系統的設計方案,該方案在25 cm×12 cm的PCB板上實現了波形產生、波形捷變與幅相控制的系統集成設計。該系統能同時產生16路頻率、幅度和相位獨立控制的中頻雷達信號,滿足數字陣列雷達對收發陣列單元的高集成度、小型化、低成本和多功能的要求;系統實現的主要技術指標為;信號帶寬1~1 20 MHz可變,通道隔離度大于60 dBc,窄帶脈內信噪比大于65 dBc,滿足數字陣列雷達技術指標的要求。

關鍵詞:數字陣列雷達;波形產生;直接數字頻率合成;小型化

0 引言

數字陣列雷達(Digital Array Radar,DAR)在接收和發射模式下均采用數字波束形成(Digital Beam Forming,DBF),實現射頻信號功率在空域靈活分配與接收,獲得優良的收發波束特性,從而提升了雷達系統的多項性能,是雷達重要發展趨勢之一。在數字陣列雷達中,直接數字頻率合成(Direct Digital Synthesizer,DDS)是實現雷達波形產生與發射波束控制的最常用的方案之一。基于DDS技術的多通道波形產生系統不僅可以方便地產生各種雷達波形,還可以在數字域靈活地對陣列天線進行相位和幅度加權,實現發射波束的快速、高精度控制,從而實現雷達波形產生、波形捷變與幅相控制的一體化設計。

1995年,Adrian Garrod提出了數字T/R組件的基本概念,研制了13單元收發全DBF相控陣雷達實驗系統,該系統采用DDS技術實現了波形產生系統,其信號樣式為線性調頻,瞬時帶寬小于1 MHz;林肯實驗室于2003年完成了一個S波段寬帶數字陣列試驗系統,該系統采用DDS技術產生線性調頻信號,擁有寬帶(500 MHz)和窄帶(10 MHz)兩種工作方式;文獻也介紹了多種采用DDS技術實現波形產生與發射DBF控制的數字陣列系統。上述文獻介紹的大都是應用于DAR實驗驗證系統中的波形產生系統,其系統結構較為復雜,系統集成度較低,成本較高;而數字陣列雷達發展尤其是大規模數字陣列的興起,對陣列單元的集成度、體積、成本和功能多樣化等方面提出了進一步的要求。本文介紹了一種基于DDS技術的多通道、小型化、低成本的波形產生系統的設計,該系統在25 cm×12 cm的PCB板上實現了16通道波形產生、波形捷變與幅相控制的一體化設計,能同時產生16路頻率、幅度和相位獨立控制的中頻雷達信號,信號帶寬1~120 MHz可變,通道隔離度大于60 dBc,該系統已成功應用于某數字陣列雷達。

1 數字波形產生原理與幅相控制方法

應用于雷達波形產生的DDS技術主要分為基于存儲器的直接數字波形合成(Direct Digital WaveformSynthesizer,DDWS)和基于累加器的直接數字頻率合成(Direct Digital Frequency Synthesizer,DDFS)兩類。DDWS技術是根據高速采樣時鐘,直接讀取預先存儲在高速存儲器中的數字波形,進行數/模轉換獲得所需模擬波形,其特點是簡單靈活,只要存儲器時鐘足夠高,叮以獲得超寬帶LFM信號,不足之處在于需要大容量存儲器,系統結構較為復雜。DDFS技術是通過相位累加器得到當前相位值,然后利用該值尋址ROM查找表,讀出相應的信號幅值,最后經數/模變換獲得模擬波形,其特點是頻率分辨率高、波形參數控制靈活,不足之處在于限于DDS器件的水平其時鐘頻率不夠高,難以產生超寬帶波形。

對于大規模數字陣列,高集成度、小型化、低成本是系統設計的關鍵問題之一。隨著數字集成電路的發展,DDFS芯片集成度和時鐘頻率進一步提高,尤其是單芯片多通道DDFS芯片的出現,給實現高集成度、小型化、低成本的陣列雷達多通道波形產生系統提供了便利。針對實際數字陣列系統指標要求產生中心頻率為140 MHz,帶寬為1~120 MHz的線性調頻,設計中采用DDFS技術實現多通道波形產生是最優的方案。

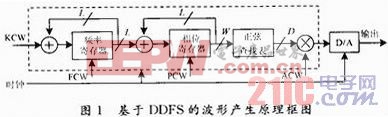

圖1給出了一種適用于數字陣列雷達基于DDFS技術的雷達波形產生系統原理框圖,DDS核中的相位累加器完成調相功能,而頻率累加器和相位累加器兩級串聯結構完成調頻功能,正弦查找表后的乘法器則完成對波形信號幅度的控制,于是實現了陣列雷達的波形產生、波形捷變和幅相控制的一體化設計。

2 多通道波形產生的實現

2.1 多通道波形產生系統結構與硬件設計

根據上文的分析,采用DDFS技術來實現該多通道波形產生系統,考慮到系統指標實現和成本要求,選用ADI公司的四通道高集成度DDS芯片AD9959作為系統的核心芯片,該芯片最高時鐘頻率達到500 MHz,包含了四路頻率、相位和幅度獨立可控的DDS核,DDS核的內部結構與圖1所示的原理框圖一致。設計中采用了4片AD9959芯片,配以外圍邏輯電路、轉換電路,在單塊PCB板上實現了16通道獨立可控的中頻雷達信號的系統集成設計,系統結構框圖如圖2所示。AD9959時鐘頻率選為480 MHz,FPGA的同步時鐘為60 MHz;采用三片FPGA組成邏輯控制電路,完成對AD9959的初始化配置,對波形控制系統送來的控制碼進行譯碼,并行計算十六路DDS通道波形的頻率、幅度、相位等控制參數,轉化為DDS寄存器控制碼,完成對16個通道相應寄存器的讀寫操作。這樣,利用AD9959的頻率和幅相控制功能,在完成數字波形信號產生的同時,對數字陣列的每個發射單元波形的頻率、相位和幅度進行獨立控制,該數字信號經D/A變換成模擬中頻信號,然后由線性上變頻通道完成發射頻率擴展形成射頻信號,最后射頻信號經天線輻射單元實現發射DBF。

評論