切換式電源的靜電放電能力防制技術

先確認因ESD而產生之故障現象,一般來說,ESD造成的故障現象包括:

1. 機臺有跳火的現象(不在規劃的放電PAD上)

2. 機臺進入保護模式(auto or latch)

3. 整個機臺損壞。

A. 若機臺有跳火的現象,一般為絕緣不足或距離不夠所致,對策方式為:

a.1可先用Hi-pot做一二次側的絕緣測試,將Hi-pot的電壓慢慢的往上調整,當一二次側的絕緣或距離不足時,即為產生跳火而致使漏電流超過10mA,Hi-pot機跳離。尤其是變壓器內部或散熱片與周邊零件的距離,用此法可快速檢測機臺一二次側之間的距離問題。

a.2將輸入端的火線/中線/地線全部接在一起下地,然后再去測ESD(機臺沒開機),此方式是檢測當有外部電荷進入時,是否電荷是依循規劃路徑在走,只在放電PAD上有跳火。用此方式可以在不傷機臺的情況下(因沒有開機)先確認組件之間的距離是否足夠,若不夠即會跳火。

a.3在ESD測試時,可關燈確認跳火現象是在哪一個部份,一般跳火可用方式為:

a.3.1增加熱縮套管,加強絕緣。

a.3.2修改layout,增加組件之間距離。

a.3.3在跳火處涂上白膠,增加其絕緣強度。

B. 若機臺進入保護模式,對策方式為

b.1先判斷與此現象相關的電路部分,看哪一部份電路動作會導致此保護現象,然后先將此保護模式關掉。例如測試ESD造成電源latch,就先將IC 會進到latch 的功能先Disable,看是否為IC周邊線路誤動作導致IC進到latch。

b.2若不是保護線路問題,即可能為IC被干擾,對IC來說,操作電流或操作電壓愈小的pin腳愈容易被干擾(pin腳呈現高阻抗),確認IC哪個腳位的操作電流很小,設法增加一小電容去濾波或在pin腳前端串聯一電阻做干擾訊號的衰減,在切換式電源IC里,CS pin因操作電壓較低,故較容易受干擾,因此CS pin的layout 要極為注意;另外,TL431的地也很重要,在規劃TL431的地時,最好連接于疏導電路的后端(讓大多的電荷先走過疏導電路再進入TL431的地),或于輸出端并聯一顆MLCC電容再接至此(讓此電容做突波的衰減)。

b.3 IC 的所有腳位不可空接, 空接的腳位很容易受外來干擾而被誤動作,需以電容或電阻連接至Vcc或接地來拉高或降低其電位。

b.4 IC的Vcc腳也可能因太大的突波而干擾IC內部運作,可串接電阻,并電容來減少突波。

b.5若仍無法找到保護問題,則需用隔離探棒同時量測gate與IC各pin之間的波形,確認是何pin誤觸IC進到保護模式。

C. 若機臺整臺損壞,對策為:

c.1機臺會損壞表示電荷疏導不足,讓電荷進入組件或IC造成損壞,先確認機臺的疏導路徑是否如之前所提,半導體組件不要經過疏導路徑,而疏導路徑的銅箔要盡量加粗來使電荷快速放電。

c.2可增加Y電容的容值,降低高頻時Y電容的阻抗,增加流過此路徑的電荷。

c.3 若IC有高壓pin,可在此腳并聯一電容來吸收突波電壓。

c.4 有些IC的輸入/輸出端很容易被打穿,在設計上要極小心;輸入即為Vcc端,前面有介紹可外加電容,電感或電阻來壓制,要注意IC的Vcc絕不能超過其最大額定值,因IC的輸出端有一個totem pole,而輸出端與Vcc存

在一個上臂的MFET,若Vcc超過此MFET的Vds即可能打穿IC的Vcc至Vgate,讓輸出一直為高電位。輸出即為驅動端,有時會因MFET較大的Cgd而讓電荷經由驅動端灌入,可于驅動端串聯一電感來抑制其突波電流,或增加一電容對地來吸收突波。

c.5注意組件的選擇與layout,對ESD的高頻線路來說,寄生電感的影響非常大,在layout 時要將power trace(大電流在走動的線路)布的愈粗,愈短愈好,以減少其寄生電感;而在組件的選擇上,偵測電阻也盡量要選用無感電阻。回路上的電感愈大,其感應的逆向電壓也愈大,此產生的逆向電壓有可能導致IC損壞。

c.6若仍找不出損壞的原因,可用一外加TVS(速度較快),并接于可能發生過電壓的地方做限壓,或并聯一二極管作負壓的放電。

結語:

ESD的防制其實重點在于放電路徑的規劃與相關原理的了解,只要在一開始做電路設計時有先考慮ESD快速放電路徑,問題就可以解決一半。而相關原理則包括了解靜電測試時的標準測試線路(一個150pF的電容與330?的串聯電阻),

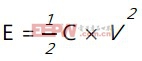

電荷公式Q=C×V與能量公式 ,

,

當電容充滿電壓并對待測物放電時,待測物上有哪些路徑會讓電荷走過?哪些組件可以幫助電荷放電,哪些組件會妨礙電荷放電,易受干擾的組件要如何接到訊號源而不受ESD干擾等,利用串聯電阻抑制突波電流與電壓,串聯電感抑制突波電流,并聯電容抑制突波電壓等方式,可改善大部份ESD造成的干擾問題。

評論